# Intel® 965 Express Chipset Family and Intel® G35 Express Chipset Graphics Controller PRM

Programmer's Reference Manual (PRM)

Volume 4: Subsystem and Cores

January 2008

Revision 1.0d

Technical queries: ilg@linux.intel.com www.intellinuxgraphics.org

#### Creative Commons License

#### You are free:

to Share — to copy, distribute, display, and perform the work

#### Under the following conditions:

**Attribution.** You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

No Derivative Works. You may not alter, transform, or build upon this work.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® 965 Express Chipset family and Intel® G35 Express Chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

I2C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I2C bus/protocol and was developed by Intel. Implementations of the I2C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and the Intel are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2008, Intel Corporation. All rights reserved.

# **Contents**

| 1 | Introd | uction         |                                                            | .19        |

|---|--------|----------------|------------------------------------------------------------|------------|

|   | 1.1    |                | s and Conventions                                          |            |

|   |        | 1.1.1          | Reserved Bits and Software Compatibility                   | .21        |

|   | 1.2    | Termino        | logy                                                       | .21        |

| 2 | Subsv  | stem Ove       | rview                                                      | .33        |

|   | 2.1    |                | tion                                                       |            |

|   | 2.1    |                | em Topology                                                |            |

|   | 2.2    | •              | n Units (EUs)                                              |            |

|   | 2.3    |                | Dispatching                                                |            |

|   |        |                | Functions                                                  |            |

|   | 2.5    |                | -unctions                                                  |            |

|   | 2.6    | 2.6.1          | Message Register File (MRF)                                |            |

|   |        | 2.6.2          | Send Instruction                                           |            |

|   |        | 2.6.3          | Creating and Sending a Message                             |            |

|   |        | 2.6.4          | Message Payload Containing a Header                        | .40        |

|   |        | 2.6.5          | Writebacks                                                 | .40        |

|   |        | 2.6.6          | Message Delivery Ordering Rules                            |            |

|   |        | 2.6.7          | Execution Mask and Messages<br>End-Of-Thread (EOT) Message |            |

|   |        | 2.6.8<br>2.6.9 | Performance                                                |            |

|   |        | 2.6.10         | Message Description Syntax                                 |            |

|   |        | 2.6.11         | Message Errors                                             |            |

| 3 | Debug  | aina           |                                                            | 45         |

|   | 3.1    |                | tion                                                       |            |

|   | 3.2    |                | pshot Mechanism                                            |            |

|   | 3.3    | 3.2.1          | Debug Trigger Counters                                     |            |

|   |        |                | nction Debug Process                                       |            |

|   |        | 3.3.1          | Overview                                                   |            |

|   |        | 3.3.2          | Vertex Shader Debug                                        |            |

|   |        | 3.3.3          | SVG Debug                                                  |            |

|   |        |                | 3.3.3.1 SVG_CTL —Debug Control                             |            |

|   |        |                | 3.3.3.2 SVG_RDATA—Debug Return Data                        |            |

|   |        | 224            | 3.3.3.3 SVG_WORK_CTL—Debug Workaround Control              |            |

|   |        | 3.3.4          | Vertex Fetch                                               |            |

|   |        |                | 3.3.4.2 VF_STRG_VAL—Debug Snapshot Trigger Value           |            |

|   |        |                | 3.3.4.3 VF_STR_VL_OVR —Debug Start Vertex Location Overrid |            |

|   |        |                | 3.3.4.4 VF_VC_OVR —Debug Vertex Count Override             |            |

|   |        |                | 3.3.4.5 VF_STR_PSKIP —Debug Starting Primitives Skipped    |            |

|   |        |                | 3.3.4.6 VF_MAX_PRIM —Debug Max Primitives                  |            |

|   |        | 335            | 3.3.4.7 VF_RDATA —Debug Return Data                        |            |

|   |        | 3.3.5          | Vertex Shader                                              | . 54<br>55 |

|   |        |                | 3.3.5.2 VS_STRG_VAL—Debug Snapshot Trigger Value           |            |

|   |        |                |                                                            |            |

|     |          | 3.3.5.3     | VS_RDATA —Debug Return Data                                   |      |

|-----|----------|-------------|---------------------------------------------------------------|------|

|     | 3.3.6    |             | Shader                                                        |      |

|     |          | 3.3.6.1     | GS_CTL —Debug Control                                         |      |

|     |          | 3.3.6.2     | GS_STRG_VAL —Debug Snapshot Trigger Value                     | . 58 |

|     |          | 3.3.6.3     | GS_RDATA —Debug Return Data                                   | . 58 |

|     | 3.3.7    | Clipper     |                                                               |      |

|     |          | 3.3.7.1     | CL CTL—Debug Control                                          | .60  |

|     |          | 3.3.7.2     | CL_STRG_VAL—Debug Snapshot Trigger Value                      |      |

|     |          | 3.3.7.3     | CL_RDATA—Debug Return Data                                    |      |

|     | 3.3.8    |             | IS                                                            |      |

|     | 3.3.0    | 3.3.8.1     | SF_CTL —Debug Control                                         |      |

|     |          |             | SF_CTL —Debug ControlSF_STRG_VAL—Debug Snapshot Trigger Value |      |

|     |          | 3.3.8.2     |                                                               |      |

|     |          | 3.3.8.3     | SF_MIN_PR_IND—Debug Minimum Primitive Index                   |      |

|     |          | 3.3.8.4     | SF_MAX_PR_IND—Debug Maximum Primitive Index                   | . 64 |

|     |          | 3.3.8.5     | SF_CLIP_RMIN- Debug Clip Rectangle Minimum                    |      |

|     |          |             | Coordinates                                                   | .65  |

|     |          | 3.3.8.6     | SF_CLIP_RMAX—Debug Clip Rectangle Maximum                     |      |

|     |          |             | Coordinates                                                   | .65  |

|     |          | 3.3.8.7     | SF_RDATA—Debug Return Data                                    | . 65 |

|     | 3.3.9    | Windower    | / Intermediate Z                                              |      |

|     |          | 3.3.9.1     | WIZ_CTL—Debug Control                                         |      |

|     |          | 3.3.9.2     | WIZ_STRG_VAL —Debug Snapshot Trigger Value                    |      |

|     |          | 3.3.9.3     | WIZ_RDATA—Debug Return Data                                   |      |

|     | 3.3.10   |             | nt End                                                        | 70   |

|     | 3.3.10   | 3.3.10.1    | VFE_CTL—Debug Control                                         |      |

|     |          | 3.3.10.1    | VFE_STRG_VAL—Debug Snapshot Trigger Value                     |      |

|     |          |             |                                                               |      |

|     | 2 2 11   | 3.3.10.3    | VFE_RDATA—Debug Return Data                                   |      |

|     | 3.3.11   |             | Dawner                                                        |      |

|     |          | 3.3.11.1    |                                                               |      |

|     |          | 3.3.11.2    | TS_STRG_0-6VAL—Debug Snapshot Trigger R0.6 Value              |      |

|     |          | 3.3.11.3    | TS_STRG_0-7VAL—Debug Snapshot Trigger R0.7 Value              |      |

|     |          | 3.3.11.4    | TS_RDATA—Debug Return Data                                    |      |

|     |          | 3.3.11.5    | Parent Thread Recommendations                                 | .74  |

| 3.4 | Shared I | Function De | ebug                                                          | . 75 |

|     | 3.4.1    |             | spatcher                                                      |      |

|     | J        | 3.4.1.1     | TD_CTL—Debug Control                                          |      |

|     |          | 3.4.1.2     | TD_CTL2—Debug Control 2                                       |      |

|     |          | 3.4.1.3     | TD_VF_VS_EMSK—Debug VF/VS Execution Mask                      |      |

|     |          | 3.4.1.4     | TD_GS_EMSK—Debug GS Execution Mask                            |      |

|     |          |             |                                                               |      |

|     |          | 3.4.1.5     | TD_CLIP_EMSK—Debug Clipper Execution Mask                     |      |

|     |          | 3.4.1.6     | TD_SF_EMSK—Debug SF Execution Mask                            |      |

|     |          | 3.4.1.7     | TD_WIZ_EMSK — Debug WIZ Execution Mask                        |      |

|     |          | 3.4.1.8     | TD_0-6_EHTRG_VAL—Debug R0.6 External Halt Trigger             |      |

|     |          |             | Value                                                         | . 78 |

|     |          | 3.4.1.9     | TD_0-7_EHTRG_VAL—Debug R0.7 External Halt Trigger             |      |

|     |          |             | Value                                                         |      |

|     |          | 3.4.1.10    | TD_0-6_EHTRG_MSK—Debug R0.6 External Halt Trigger             | •    |

|     |          |             | Mask                                                          |      |

|     |          | 3.4.1.11    | TD_0-7_EHTRG_MSK—Debug R0.7 External Halt Trigger             |      |

|     |          |             | Mask                                                          |      |

|     |          | 3.4.1.12    | TD_RDATA—Debug Return Data                                    |      |

|     |          | 3.4.1.13    | TD TS EMSK—Debug TS Execution Mask                            |      |

|     | 3.4.2    |             |                                                               |      |

|     | J. 1.2   | 3.4.2.1     | MATH_CTL—Math Debug Control                                   |      |

|     |          | 3.4.2.2     | MATH_CTL—Math Debug Control                                   |      |

|     |          | J.サ.と.と     | INATH NUMBATION DEDUK RELUIT DALA                             | . 02 |

|   |        | 3.4.3     |                    | n / State Cache82                                              |

|---|--------|-----------|--------------------|----------------------------------------------------------------|

|   |        | 2 4 4     | 3.4.3.1            | ISC_CTL—Instruction / State Debug Control82                    |

|   |        | 3.4.4     | 3.4.4.1            | n L1 Cache83 ISC_L1CA_CTR—Instruction L1 Cache Debug Control83 |

|   |        |           | 3.4.4.2            | ISC_L1CA_RDATA—Instruction L1 Cache Debug Return               |

|   |        |           | 31 11 112          | Data83                                                         |

|   |        |           | 3.4.4.3            | ISC_L1CA_BP_ADR1—Instruction L1 Cache Breakpoint               |

|   |        |           |                    | Address 1 Control84                                            |

|   |        |           | 3.4.4.4            | ISC_L1CA_BP_ADR2—Instruction L1 Cache Breakpoint               |

|   |        |           | 2445               | Address 2 Control84                                            |

|   |        |           | 3.4.4.5            | ISC_L1CA_BP_OPC1—Instruction L1 Cache Breakpoint               |

|   |        |           | 3.4.4.6            | Opcode 1 Control                                               |

|   |        |           | 3.4.4.0            | Opcode 2 Control85                                             |

|   |        | 3.4.5     | Message A          | Arbiter86                                                      |

|   |        |           | 3.4.5.1            | MA_DEBUG_1—Message Arbiter Debug Control87                     |

|   |        | 3.4.6     | Sampler            | 88                                                             |

|   |        |           | 3.4.6.1            | SAMPLER_CTL—Sampler Debug Control88                            |

|   |        |           | 3.4.6.2            | SAMPLER_RDATA—Sampler Debug Return Data89                      |

|   |        | 3.4.7     |                    | DD CTI Data Data Data Control                                  |

|   |        |           | 3.4.7.1<br>3.4.7.2 | DP_CTL—Data Port Debug Control                                 |

|   |        | 3.4.8     | _                  | ache91                                                         |

|   |        | 3. 1.0    | 3.4.8.1            | RC CTL—RC Debug Control91                                      |

|   |        |           | 3.4.8.2            | RC_DEF_CLR—RC Debug Force Default Color91                      |

|   |        |           | 3.4.8.3            | RC_RDATA—RC Debug Return Data92                                |

|   |        | 3.4.9     |                    | eturn Buffer (URB)92                                           |

|   |        |           | 3.4.9.1            | URB_CTL—URB Debug Control92                                    |

|   |        | 2 4 10    | 3.4.9.2            | URB_RDATA—URB Debug Return Data93                              |

|   | 3.5    | 3.4.10    | -                  | pawner (TS)                                                    |

|   | 3.5    | 3.5.1     |                    | from EU to Host                                                |

|   |        | 3.5.2     |                    | EU Debug Attention95                                           |

|   |        | 3.5.3     |                    | DATA—EU Debug Attention Data95                                 |

|   |        | 3.5.4     |                    | CLR—EU Debug Attention Clear96                                 |

|   |        | 3.5.5     | EU_RDAT            | A—EU Debug Return Data96                                       |

|   | 3.6    | Breakpoi  | nts                | 97                                                             |

|   |        | 3.6.1     |                    | epping97                                                       |

|   |        | 3.6.2     |                    | on of Instruction Stream98                                     |

|   | 3.7    | Message   |                    | 98                                                             |

|   |        |           |                    | Error-Types Visible to the Arb                                 |

|   |        |           | 3.7.1.2            | Non-pipelined S/F Operation99                                  |

| 4 | Sampli | ng Engine | <u> </u>           |                                                                |

|   | 4.1    | Texture ( | Coordinate         | Processing                                                     |

|   |        | 4.1.1     |                    | oordinate Normalization102                                     |

|   |        | 4.1.2     |                    | oordinate Computation 102                                      |

|   | 4.2    | Texel Ad  | dress Gene         | eration 103                                                    |

|   |        | 4.2.1     | Level of D         | etail Computation (Mipmapping)104                              |

|   |        |           | 4.2.1.1            | Base Level Of Detail (LOD)104                                  |

|   |        |           | 4.2.1.2            | LOD Bias                                                       |

|   |        |           | 4.2.1.3            | LOD Pre-Clamping                                               |

|   |        |           | 4.2.1.4<br>4.2.1.5 | Min/Mag Determination                                          |

|   |        |           | ±.∠.1.J            | LOD Computation r seduocode                                    |

|   |         | 4.2.2     | Inter-Leve | el Filtering Setup            | 107 |

|---|---------|-----------|------------|-------------------------------|-----|

|   |         | 4.2.3     |            | el Filtering Setup            |     |

|   |         |           | 4.2.3.1    | MAPFILTER_NEAREST             |     |

|   |         |           | 4.2.3.2    | MAPFILTER_LINEAR              |     |

|   |         |           | 4.2.3.3    | MAPFILTER_ANISOTROPIC         | 109 |

|   |         |           | 4.2.3.4    | MAPFILTER_MONO                |     |

|   |         | 4.2.4     | Texture A  | ddress Control                |     |

|   |         |           | 4.2.4.1    | TEXCOORDMODE_WRAP Mode        |     |

|   |         |           | 4.2.4.2    | TEXCOORDMODE_MIRROR Mode      |     |

|   |         |           | 4.2.4.3    | TEXCOORDMODE_MIRROR_ONCE Mode |     |

|   |         |           | 4.2.4.4    | TEXCOORDMODE CLAMP Mode       |     |

|   |         |           | 4.2.4.5    | TEXCOORDMODE CLAMPBORDER Mode |     |

|   |         |           | 4.2.4.6    | TEXCOORDMODE_CUBE Mode        |     |

|   | 4.3     | Texel Fet |            |                               |     |

|   |         | 4.3.1     |            | oma Keying                    |     |

|   |         | 4.5.1     | 4.3.1.1    | Chroma Key Testing            |     |

|   |         |           | 4.3.1.2    | Chroma Key Effects            |     |

|   | 4.4     | Chadow    | _          | •                             |     |

|   |         |           |            | ompare                        |     |

|   | 4.5     |           | _          |                               |     |

|   | 4.6     | Texel Co  | lor Gamma  | a Linearization               | 117 |

|   | 4.7     | State     |            |                               | 118 |

|   |         | 4.7.1     | BINDING    | _TABLE_STATE                  | 118 |

|   |         | 4.7.2     |            |                               |     |

|   |         |           | 4.7.2.1    | For Most Messages             |     |

|   |         | 4.7.3     |            | STATE                         |     |

|   |         |           | 4.7.3.1    | For Most Messages             |     |

|   |         | 4.7.4     | SAMPLER    | _BORDER_COLOR_STATE           |     |

|   |         | 4.7.5     |            | CHROMA_KEY                    |     |

|   |         | 4.7.6     |            |                               |     |

|   | 4.8     |           |            |                               |     |

|   |         | 4.8.1     |            | Message                       |     |

|   |         | 4.0.1     | 4.8.1.1    | Message Descriptor            |     |

|   |         |           | 4.8.1.2    | Message Header                |     |

|   |         |           | 4.8.1.3    | Payload Parameter Definition  |     |

|   |         |           | 4.8.1.4    | Message Types                 |     |

|   |         |           | 4.8.1.5    | Parameter Types               |     |

|   |         |           | 4.8.1.6    | SIMD16 Payload                |     |

|   |         |           | 4.8.1.7    | SIMD8 Payload                 |     |

|   |         |           | 4.8.1.8    | SIMD4x2 Payload               |     |

|   |         | 4.8.2     |            | Message                       |     |

|   |         | 11012     | 4.8.2.1    | SIMD16                        |     |

|   |         |           | 4.8.2.2    | SIMD8                         |     |

|   |         |           | 4.8.2.3    | SIMD4x2                       |     |

|   |         |           |            |                               |     |

| 5 | Data Po | ort       |            |                               | 171 |

|   | 5.1     | Cache Ad  | ients      |                               | 171 |

|   | 3.1     | 5.1.1     |            | ache                          |     |

|   |         | 5.1.2     |            | ne                            |     |

|   |         | 5.1.2     |            | Cache                         |     |

|   | 5.2     |           | •          | Jacile                        |     |

|   | J. Z    |           |            |                               |     |

|   |         | 5.2.1     |            | tate Model                    |     |

|   | F 2     | 5.2.2     |            | Model                         |     |

|   | 5.3     | write Co  | mmıt       |                               | 1/3 |

|   | 5.4         | Read/Wr   | ite Orderin          | ıg                                       | 174 |

|---|-------------|-----------|----------------------|------------------------------------------|-----|

|   | 5.5         | Accessin  | g Buffers            |                                          | 174 |

|   | 5.6         | Accessin  | a Media Su           | ırfaces                                  | 175 |

|   |             | 5.6.1     | _                    | Behavior                                 |     |

|   | 5.7         | Accessin  |                      | argets                                   |     |

|   |             | 5.7.1     | _                    | urce                                     |     |

|   |             | 5.7.2     |                      | rce [DevCL-B]                            |     |

|   |             | 5.7.3     |                      | Data                                     |     |

|   |             | 5.7.4     | Multiple R           | lender Targets (MRT)                     | 177 |

|   | 5.8         | Flushing  | the Rende            | r Cache                                  | 177 |

|   | 5.9         | State     |                      |                                          | 177 |

|   |             | 5.9.1     | BINDING              | _TABLE_STATE                             | 177 |

|   |             | 5.9.2     | SURFACE              | _STATE                                   | 177 |

|   | 5.10        | Message   | s                    |                                          | 178 |

|   |             | 5.10.1    | Global De            | finitions                                | 178 |

|   |             |           | 5.10.1.1             | Message Descriptor                       | 179 |

|   |             |           | 5.10.1.2             | Message Header                           |     |

|   |             |           |                      | Write Commit Writeback Message           |     |

|   |             | 5.10.2    |                      | ock Read/Write                           |     |

|   |             |           | 5.10.2.1             | Message Descriptor                       |     |

|   |             |           | 5.10.2.2             | Message Payload (Write)                  |     |

|   |             | E 10 2    |                      | Writeback Message (Read)                 |     |

|   |             | 5.10.3    | 5.10.3.1             | ual Block Read/Write  Message Descriptor |     |

|   |             |           | 5.10.3.1             | Message Payload                          |     |

|   |             |           | 5.10.3.3             | Additional Message Payload (Write)       |     |

|   |             |           | 5.10.3.4             | Writeback Message (Read)                 |     |

|   |             | 5.10.4    |                      | ck Read/Write                            |     |

|   |             |           | 5.10.4.1             | Message Descriptor                       |     |

|   |             |           | 5.10.4.2             | Message Header                           | 189 |

|   |             |           | 5.10.4.3             | Message Payload (Write)                  |     |

|   |             |           | 5.10.4.4             | Writeback Message (Read)                 |     |

|   |             | 5.10.5    |                      | cattered Read/Write                      |     |

|   |             |           | 5.10.5.1             | Message Descriptor                       |     |

|   |             |           | 5.10.5.2             | Message Payload                          |     |

|   |             |           | 5.10.5.3             | Additional Message Payload (Write)       |     |

|   |             | 5.10.6    | 5.10.5.4             | Writeback Message (Read)arget Write      |     |

|   |             | 3.10.0    | 5.10.6.1             | Subspan/Pixel to Slot Mapping            |     |

|   |             |           | 5.10.6.2             | Message Descriptor                       |     |

|   |             |           | 5.10.6.3             | Message Header                           |     |

|   |             |           | 5.10.6.4             | Stencil and Antialias Alpha Payload      |     |

|   |             |           | 5.10.6.5             |                                          |     |

|   |             |           | 5.10.6.6             | ,                                        |     |

|   |             |           | 5.10.6.7             |                                          |     |

|   |             |           | 5.10.6.8             |                                          |     |

|   |             | F 40 7    | 5.10.6.9             |                                          |     |

|   |             | 5.10.7    |                      | der Cache                                |     |

|   |             |           | 5.10.7.1<br>5.10.7.2 | Message Descriptor                       |     |

|   |             |           |                      | Message Payload                          |     |

| 6 | Extend      | ed Math . |                      |                                          | 211 |

|   | 6.1         | Message   | S                    |                                          | 212 |

|   | <del></del> | 6.1.1     |                      | Message                                  |     |

|   |             |           |                      | <b>J</b>                                 |     |

|    |         |                | 6.1.1.1<br>6.1.1.2<br>6.1.1.3 | Message Descriptor                       | 213 |

|----|---------|----------------|-------------------------------|------------------------------------------|-----|

|    |         | 6.1.2          |                               | Message                                  |     |

|    | 6.2     |                |                               | nessage                                  |     |

|    | 6.3     |                |                               |                                          |     |

|    | 0.5     | 6.3.1          |                               |                                          | _   |

|    |         | 6.3.2          |                               |                                          |     |

|    |         | 6.3.3          |                               |                                          |     |

|    |         | 6.3.4          | SQRT                          |                                          | 221 |

|    |         | 6.3.5          | -                             |                                          |     |

|    |         | 6.3.6          |                               |                                          |     |

|    |         | 6.3.7          | _                             |                                          |     |

|    |         | 6.3.8<br>6.3.9 |                               |                                          |     |

|    |         | 6.3.10         |                               |                                          |     |

| 7  | Massass |                |                               |                                          |     |

| /  |         |                |                               |                                          |     |

|    | 7.1     | _              |                               |                                          |     |

|    |         | 7.1.1          |                               | Descriptor                               |     |

|    |         | 7.1.2          | 7.1.2.1                       | way Message Message Payload              |     |

|    |         |                | 7.1.2.1                       | Writeback Message                        |     |

|    |         | 7.1.3          |                               | way Message                              |     |

|    |         |                | 7.1.3.1                       | Message Payload                          |     |

|    |         |                | 7.1.3.2                       | Writeback Message                        |     |

|    |         | 7.1.4          |                               | sg Message                               |     |

|    |         |                | 7.1.4.1                       | Message Payload                          |     |

|    |         |                | 7.1.4.2<br>7.1.4.3            | Writeback Message to Requester Thread    |     |

|    |         | 7.1.5          |                               | tamp Message                             |     |

|    |         | ,              | 7.1.5.1                       | Message Payload                          |     |

|    |         |                | 7.1.5.2                       | Writeback Message to Requester Thread    | 238 |

| 8  | Unified | Return B       | uffer (URB                    | )                                        | 240 |

|    | 8.1     | URB Size       | ·                             |                                          | 240 |

|    | 8.2     |                |                               |                                          |     |

|    | 8.3     |                |                               |                                          |     |

|    | 8.4     |                |                               |                                          |     |

|    | 0. 1    | 8.4.1          |                               | Mask                                     |     |

|    |         | 8.4.2          |                               | Descriptor                               |     |

|    |         | 8.4.3          |                               | TE                                       | 245 |

|    |         |                | 8.4.3.1                       | URB_WRITE Message Header                 |     |

|    |         |                | 8.4.3.2                       | URB_WRITE Message Payload                |     |

|    |         |                | 8.4.3.3                       | Writeback Message for URB Entry Allocate | 250 |

| 9  | Executi | ion Unit Is    | SA                            |                                          | 252 |

|    | 9.1     | Introduct      | tion                          |                                          | 252 |

|    |         | 9.1.1          |                               | and Scope                                |     |

|    |         | 9.1.2          |                               | d Acronyms                               |     |

|    |         | 9.1.3          | Formats a                     | nd Conventions                           | 255 |

| 10 | EU Dat  | a Types        |                               |                                          | 258 |

|    | 10 1    | Fundame        | ntal Data                     | Tynes                                    | 258 |

|    | 10.2    | Numerical Data Types2 |                                                                  |     |  |

|----|---------|-----------------------|------------------------------------------------------------------|-----|--|

|    |         | 10.2.1                | Unsigned Integers                                                | 260 |  |

|    |         | 10.2.2                | Signed Integers                                                  |     |  |

|    |         | 10.2.3                | Single Precision Floating-Point Numbers                          |     |  |

|    |         | 10.2.4                | Packed Signed Half-Byte Integer Vector                           |     |  |

|    |         | 10.2.5                | Packed 8-bit Restricted Float Vector                             |     |  |

|    | 10.3    | Floating              | Point Modes                                                      | 264 |  |

|    |         | 10.3.1                | IEEE Floating Point Mode                                         |     |  |

|    |         |                       | 10.3.1.1 Partial Listing of Honored IEEE-754 Rules               |     |  |

|    |         |                       | 10.3.1.2 Complete Listing of Deviations or Additional Requiremen |     |  |

|    |         |                       | vs. IEEE-754                                                     |     |  |

|    |         |                       | 10.3.1.3 Comparison of Floating Point Numbers                    | 266 |  |

|    |         |                       | 10.3.1.4 Min/Max of Floating Point Numbers                       | 268 |  |

|    |         | 10.3.2                | Alternative Floating Point Mode                                  | 272 |  |

|    | 10.4    | Type Cor              | nversion                                                         | 274 |  |

|    |         | 10.4.1                | Float to Integer                                                 | 274 |  |

|    |         | 10.4.2                | Integer to Integer with Same or Higher Precision                 | 274 |  |

|    |         | 10.4.3                | Integer to Integer with Lower Precision                          |     |  |

|    |         | 10.4.4                | Integer to Float                                                 | 275 |  |

| 11 | Evocuti | ion Enviro            | onment                                                           | 276 |  |

| 11 |         |                       |                                                                  |     |  |

|    | 11.1    |                       | N                                                                |     |  |

|    | 11.2    | =                     | Usage Models                                                     |     |  |

|    |         | 11.2.1                | AOS and SOA Data Structures                                      |     |  |

|    |         | 11.2.2                | SIMD4 Mode of Operation                                          |     |  |

|    |         | 11.2.3                | SIMD4x2 Mode of Operation                                        |     |  |

|    |         | 11.2.4                | SIMD16 Mode of Operation                                         |     |  |

|    | 44.0    | 11.2.5                | SIMD8 Mode of Operation                                          |     |  |

|    | 11.3    | _                     | s and Register Regions                                           |     |  |

|    |         | 11.3.1                | Register Files                                                   |     |  |

|    |         | 11.3.2                | GRF Registers                                                    |     |  |

|    |         | 11.3.3                | MRF Registers                                                    |     |  |

|    |         | 11.3.4                | ARF Registers                                                    |     |  |

|    |         |                       | 11.3.4.1 Overview                                                |     |  |

|    |         |                       | 11.3.4.2 Access Granularity                                      |     |  |

|    |         |                       | 11.3.4.3 Null Register                                           | 207 |  |

|    |         |                       | 11.3.4.4 Address Register                                        |     |  |

|    |         |                       | 11.3.4.6 Flag Register                                           |     |  |

|    |         |                       | 11.3.4.7 Mask Registers                                          |     |  |

|    |         |                       | 11.3.4.8 Mask Stack Register                                     | 297 |  |

|    |         |                       | 11.3.4.9 Mask Stack Depth Register                               |     |  |

|    |         |                       | 11.3.4.10 State Registers                                        |     |  |

|    |         |                       | 11.3.4.11 Control Register                                       |     |  |

|    |         |                       | 11.3.4.12 Notification Registers                                 |     |  |

|    |         |                       | 11.3.4.13 IP Register                                            |     |  |

|    |         | 11.3.5                | Immediate                                                        |     |  |

|    |         | 11.3.6                | Region Parameters                                                |     |  |

|    |         | 11.3.7                | Region Addressing Modes                                          |     |  |

|    |         | -                     | 11.3.7.1 Direct Register Addressing                              |     |  |

|    |         |                       | 11.3.7.2 Register-indirect Register Addressing with a 1x1 Index  |     |  |

|    |         |                       | Region                                                           | 323 |  |

|    |         |                       | 11.3.7.3 Register-indirect Register Addressing with a Vx1 Index  |     |  |

|    |         |                       | Region                                                           | 324 |  |

|    |          |                  |              | Register-indirect Register Addressing with a VXH Index |     |

|----|----------|------------------|--------------|--------------------------------------------------------|-----|

|    |          |                  |              | Region                                                 |     |

|    |          | 11.3.8           |              | des                                                    |     |

|    |          | 11.3.9           |              | Data Type                                              |     |

|    |          | 11.3.10          |              | egion Restrictions                                     |     |

|    |          |                  |              | Examples                                               |     |

|    |          | 11 2 11          |              | Different Raw Moves                                    |     |

|    |          | 11.3.11          |              | n Operand Description                                  |     |

|    | 11 /     | CIMD F           |              | Destination Region Parameters                          |     |

|    | 11.4     |                  |              | trol                                                   |     |

|    |          | 11.4.1           |              | 1                                                      |     |

|    |          | 11.4.2           |              | tion                                                   |     |

|    |          | 11.4.3           |              | with Horizontal Combination                            |     |

|    | 44 -     | 11.4.4           |              | with Vertical Combination                              |     |

|    | 11.5     |                  |              | ssion                                                  |     |

|    |          | 11.5.1           |              | and Expected Usage                                     |     |

|    |          | 11.5.2           |              | Behavior                                               |     |

|    |          | 11.5.3           |              | Restrictions                                           |     |

|    |          | 11.5.4           |              | mples                                                  |     |

|    | 11.6     |                  |              |                                                        |     |

|    | 11.7     | Creating         | Conditiona   | Flags                                                  | 345 |

|    | 11.8     | Destinati        | ion Hazard . |                                                        | 348 |

|    | 11.9     | Non-pres         | sent Operar  | nds                                                    | 348 |

|    | 11.10    | •                | •            |                                                        |     |

|    | _        |                  |              |                                                        |     |

| 12 | Except   | ions             |              |                                                        | 350 |

|    | 12.1     | Introduc         | tion         |                                                        | 350 |

|    | 12.2     |                  |              | rchitectural Registers                                 |     |

|    |          | -                |              | _                                                      |     |

|    | 12.3     |                  |              |                                                        |     |

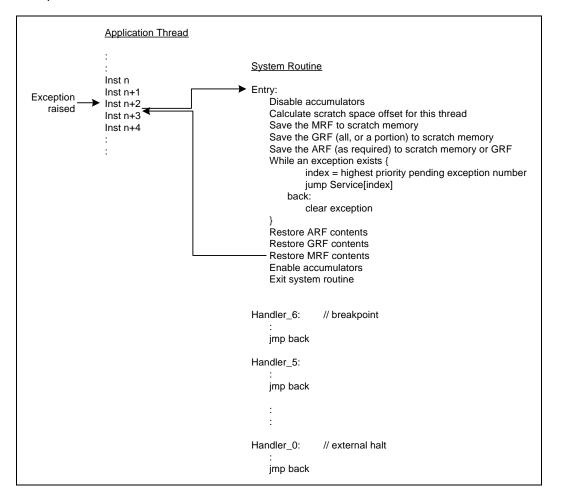

|    |          | 12.3.1           |              | ow of the System Routine                               |     |

|    |          | 12.3.2           |              | he System Routine                                      |     |

|    |          | 12.3.3           |              | to the Application Thread                              |     |

|    |          | 12.3.4           |              | (SIP)                                                  |     |

|    |          | 12.3.5<br>12.3.6 |              | outine Register Space                                  |     |

|    |          | 12.3.6           | Conditions   | ratch Memory Space                                     | 224 |

|    |          | 12.3.7           | Mossages     | in System Routinesin System Routines                   | 200 |

|    |          | 12.3.6           |              | DDClr'                                                 |     |

|    | 12.4     |                  |              |                                                        |     |

|    | 12.4     | •                | •            | ns                                                     |     |

|    |          |                  |              | code                                                   |     |

|    |          | 12.4.2           |              | opcode                                                 |     |

|    |          | 12.4.3           |              | Overflow / Underflow                                   |     |

|    |          | 12.4.4           |              | xception                                               |     |

|    |          | 12.4.5           |              | - It                                                   |     |

|    | 40.5     | 12.4.6           |              | alt                                                    |     |

|    | 12.5     |                  |              | t Generate Exceptions                                  |     |

|    | 12.6     | System I         | Handler Exa  | mple                                                   | 360 |

| 13 | Inctrice | rtion Cat C      | Summanı      |                                                        | 26  |

| 13 |          |                  |              |                                                        |     |

|    | 13.1     |                  |              | acteristics                                            |     |

|    |          | 13.1.1           | SIMD Insti   | ructions and SIMD Width                                | 364 |

|    |          |                  |              |                                                        |     |

|    |          | 13.1.2<br>13.1.3 |              | Operands and Register Regions                          |     |

|    | 13.2    | Instruction | on Machine Formats                       |     |

|----|---------|-------------|------------------------------------------|-----|

|    |         | 13.2.1      | Common Instruction Fields                | 368 |

|    |         | 13.2.2      | Instruction Operation Doubleword (DW0)   | 374 |

|    |         | 13.2.3      | Instruction Destination Doubleword (DW1) |     |

|    |         | 13.2.4      | Instruction Source-0 Doubleword (DW2)    | 383 |

|    |         | 13.2.5      | Instruction Source-1 Doubleword (DW3)    | 387 |

|    | 13.3    | Opcode I    | Encoding                                 |     |

|    |         | 13.3.1      | Move and Logic Instructions              |     |

|    |         | 13.3.2      | Flow Control Instructions                |     |

|    |         | 13.3.3      | Miscellaneous Instructions               |     |

|    |         | 13.3.4      | Parallel Arithmetic Instructions         |     |

|    |         | 13.3.5      | Vector Arithmetic Instructions           |     |

|    |         | 13.3.6      | Special Instructions                     |     |

|    | 13.4    |             | nstruction BNF                           |     |

|    | 13.7    | 13.4.1      | Instruction Groups                       |     |

|    |         | 13.4.1      | Destination Register                     |     |

|    |         | 13.4.2      | Source Register                          |     |

|    |         | 13.4.3      |                                          |     |

|    |         | 13.4.4      | Address Registers                        |     |

|    |         |             | Relative Location and Stack Control      |     |

|    |         | 13.4.6      |                                          |     |

|    |         | 13.4.7      | Regions                                  |     |

|    |         | 13.4.8      | Types                                    |     |

|    |         | 13.4.9      | Write Mask                               |     |

|    |         |             | Swizzle Control                          |     |

|    |         |             | Immediate Values                         |     |

|    |         |             | Predication and Modifiers                |     |

|    |         |             | Instruction Options                      |     |

|    | 13.5    | -           | red Features                             |     |

|    |         | 13.5.1      | Defeatured Instructions                  |     |

|    |         | 13.5.2      | Others                                   | 408 |

| 14 | Instruc | tion Set F  | Reference                                | 410 |

|    |         |             |                                          |     |

|    | 14.1    |             | ons                                      |     |

|    |         | 14.1.1      | Pseudo Code Format                       |     |

|    |         | 14.1.2      | General Macros and Definitions           |     |

|    |         | 14.1.3      | Mask Stack Operations                    |     |

|    | 14.2    | Instruction | on Description                           |     |

|    |         | 14.2.1      | add – Addition                           |     |

|    |         | 14.2.2      | and – Logical And                        |     |

|    |         | 14.2.3      | asr – Arithmetic Shift Right             | 419 |

|    |         | 14.2.4      | avg – Average                            |     |

|    |         | 14.2.5      | break – Break                            |     |

|    |         | 14.2.6      | cmp – Compare                            | 425 |

|    |         | 14.2.7      | cmpn – Compare NaN                       |     |

|    |         | 14.2.8      | cont – Continue                          | 429 |

|    |         | 14.2.9      | do – Do                                  | 431 |

|    |         | 14.2.10     | dp2 – Dot Product 2                      | 432 |

|    |         |             | dp3 – Dot Product 3                      |     |

|    |         | 14.2.12     | dp4 – Dot Product 4                      | 436 |

|    |         |             | dph -Dot Product Homogeneous             |     |

|    |         |             | else – Else                              |     |

|    |         | 14.2.15     | endif – End-If                           | 442 |

|    |         |             | frc – Fraction                           |     |

|    |         |             | halt – Halt                              |     |

|    |         |             |                                          |     |

|    |        | 14.2.18  | if – If                                                     | . 448 |

|----|--------|----------|-------------------------------------------------------------|-------|

|    |        | 14.2.19  | iff – Fast-If                                               | . 450 |

|    |        | 14.2.20  | jmpi – Jump Indexed                                         | . 452 |

|    |        |          | line – Line                                                 |       |

|    |        |          | Izd – Leading Zero Detection                                |       |

|    |        |          | mac – Multiply Accumulate                                   |       |

|    |        |          | mach – Multiply Accumulate High                             |       |

|    |        |          | mov – Move                                                  |       |

|    |        |          | mrest – Mask Restore                                        |       |

|    |        |          | msave – Mask Save                                           |       |

|    |        |          | mul – Multiply                                              |       |

|    |        |          | nop – No Operation                                          |       |

|    |        |          | not – Logic Not                                             |       |

|    |        |          | or – Logic Or                                               |       |

|    |        |          | pop – Mask Stack Pop                                        |       |

|    |        |          | push – Mask Stack Push                                      |       |

|    |        |          | rndd – Round Down                                           |       |

|    |        |          |                                                             |       |

|    |        |          | rndu – Round Up                                             |       |

|    |        |          | rnde – Round to Even                                        |       |

|    |        | 14.2.3/  | rndz – Round to Zero                                        | . 480 |

|    |        |          | sad2 – Sum of Absolute Difference 2                         |       |

|    |        |          | sada2 – Sum of Absolute Difference Accumulate 2             |       |

|    |        |          | sel – Select                                                |       |

|    |        |          | send – Send Message                                         |       |

|    |        |          | shl – Shift Left                                            |       |

|    |        |          | shr – Shift Right                                           |       |

|    |        |          | wait – Wait Notification                                    |       |

|    |        | 14.2.45  | while – While                                               | . 500 |

|    |        | 14.2.46  | xor – Logic Xor                                             | . 502 |

| 15 | EU Pro | gramming | g Guide                                                     | . 504 |

|    | 15.1   | Assemble | er Pragmas                                                  | 504   |

|    | 13.1   | 15.1.1   | Declarations                                                |       |

|    |        | 15.1.1   | Defaults and Defines                                        |       |

|    |        | _        |                                                             |       |

|    |        | 15.1.3   | Example Pragma Usages                                       |       |

|    |        | 15.1.4   | Assembly Programming Guideline                              |       |

|    | 15.2   | _        | kamples                                                     |       |

|    |        | 15.2.1   | Vector Immediate                                            |       |

|    |        |          | 15.2.1.1 Supporting Pixel Shader Indexing                   |       |

|    |        |          | 15.2.1.2 Supporting OpenGL Vertex Shader Instruction SWZ    | . 510 |

|    |        | 15.2.2   | Destination Mask for DP4 and Destination Dependency Control | . 511 |

|    |        | 15.2.3   | Null Register as the Destination                            | . 512 |

|    |        | 15.2.4   | Use of LINE Instruction                                     | . 513 |

|    |        | 15.2.5   | Mask for SEND Instruction                                   |       |

|    |        |          | 15.2.5.1 Channel Enables for Extended Math Unit             |       |

|    |        |          | 15.2.5.2 Channel Enables for Scratch Memory                 |       |

|    |        | 15.2.6   | Flow Control Instructions                                   |       |

|    |        | 15.2.7   | Execution Masking                                           |       |

|    |        | 15.2.7   | 15.2.7.1 Branching                                          |       |

|    |        |          | 15.2.7.2 Fast-If                                            |       |

|    |        |          | 15.2.7.3 Cascade Branching                                  |       |

|    |        |          | 15.2.7.4 Compound Branches                                  |       |

|    |        |          |                                                             |       |

|    |        |          | 15.2.7.5 Looping                                            |       |

|    |        |          | 15.2.7.6 Indexed Jump                                       | . JZ6 |

# **Figures**

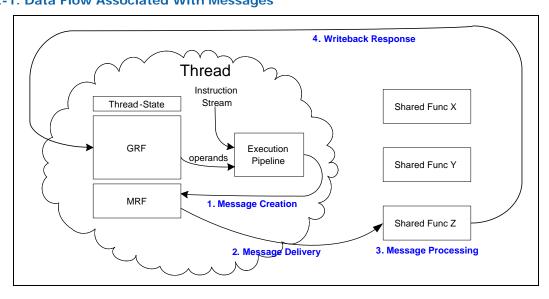

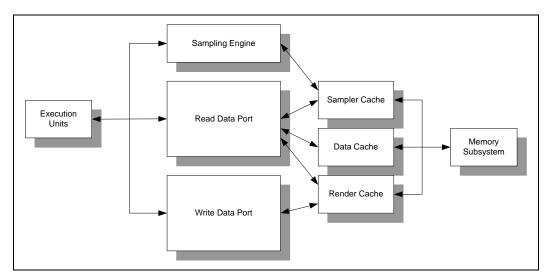

| Figure 2-1. Data Flow Associated With Messages37                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

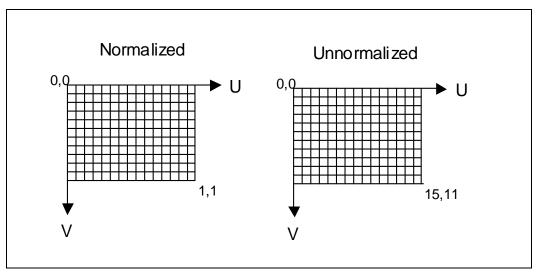

| Figure 4-1. Normalized vs. Unnormalized Texture Coordinates                                                                                                       |

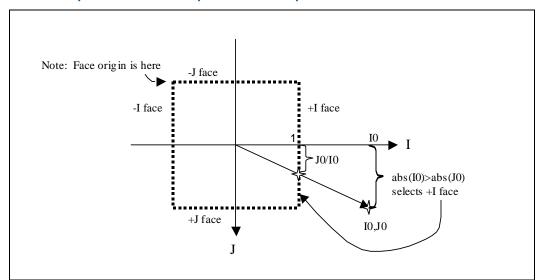

| Figure 4-2. Cube Map Coordinate Computation Example                                                                                                               |

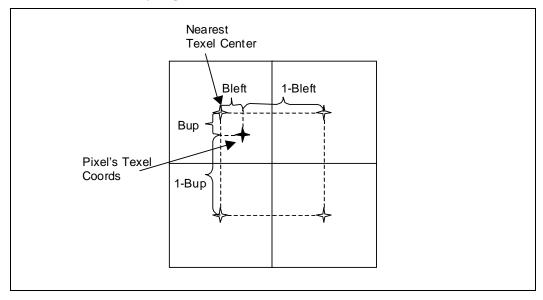

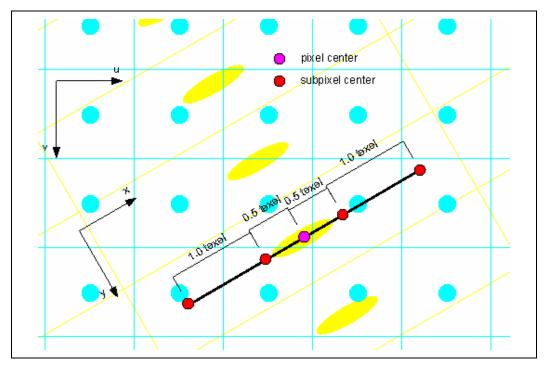

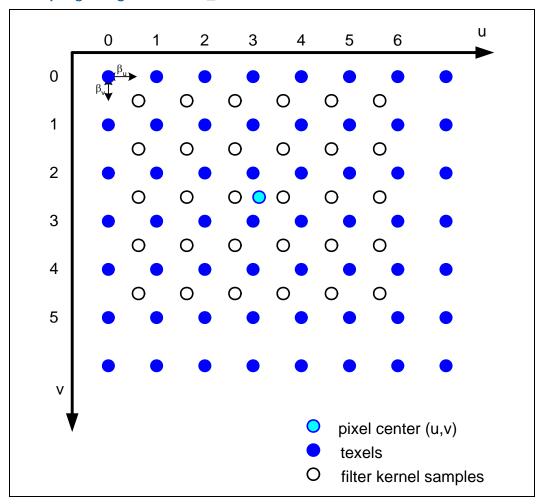

| Figure 4-3. Bilinear Filter Sampling109                                                                                                                           |

| Figure 4-4. Sampling Using MAPFILTER_MONO111                                                                                                                      |

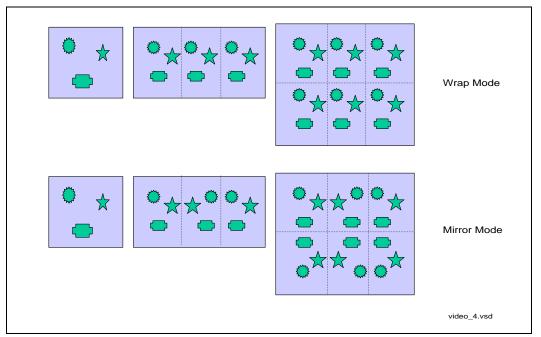

| Figure 4-5. Texture Wrap vs. Mirror Addressing Mode                                                                                                               |

| Figure 4-6. Texture Clamp Mode                                                                                                                                    |

| Figure 10-1. Fundamental data types                                                                                                                               |

| Figure 10-2. Integer numerical data types                                                                                                                         |

| Figure 10-3. Floating point numerical data types259                                                                                                               |

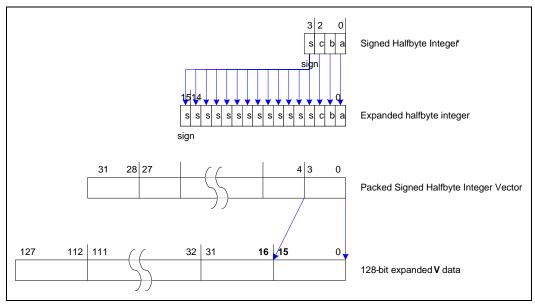

| Figure 10-4. Converting a Packed Half-byte Vector to a 128-bit Signed Integer Vector261                                                                           |

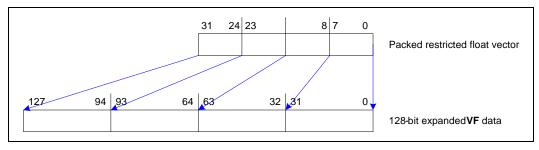

| Figure 10-5. Conversion from a Restricted 8-bit Float to a Single-Precision Float 262                                                                             |

| Figure 10-6. Converting a Packed Restricted Float Vector to a 128-bit Float Vector 264                                                                            |

| Figure 11-1. AOS and SOA data structures                                                                                                                          |

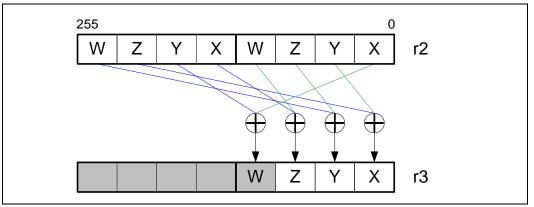

| Figure 11-2. A SIMD4 Example                                                                                                                                      |

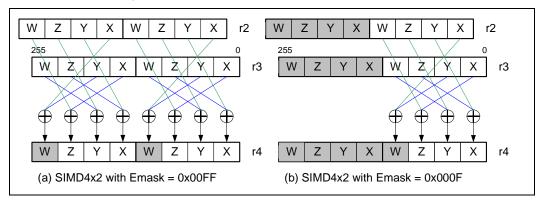

| Figure 11-3. SIMD4x2 Examples with Different Emasks                                                                                                               |

| Figure 11-4. A SIMD4x2 Example with a Constant Vector Shared by Two Program                                                                                       |

| Flows                                                                                                                                                             |

| Figure 11-5. A SIMD16 Example                                                                                                                                     |

| Figure 11-6. Another SIMD16 Example with an AOS Shared Constant                                                                                                   |

| Figure 11-7. Format of the Mask Stack Register                                                                                                                    |

| Figure 11-8. Format of the Mask Stack Depth Register                                                                                                              |

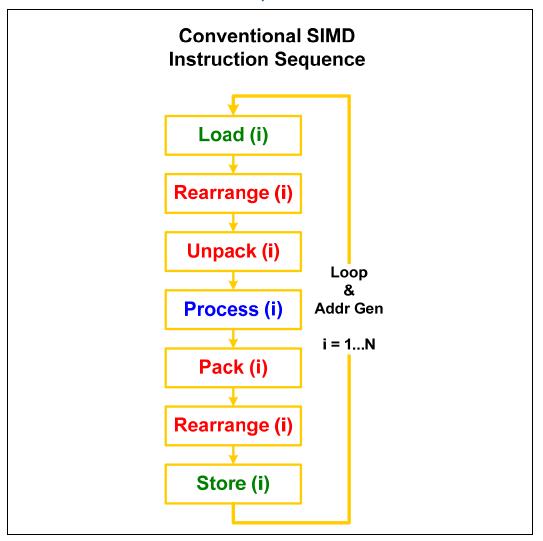

| Figure 11-9. Conventional SIMD Instruction Sequence                                                                                                               |

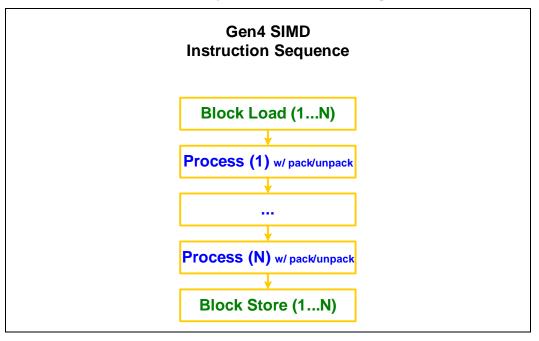

| Figure 11-10. GEN4 SIMD Instruction Sequence for the Same Program                                                                                                 |

| Figure 11-11. An example of a register region $(r4.1<16;8,2>:w)$ with 16 elements 320                                                                             |

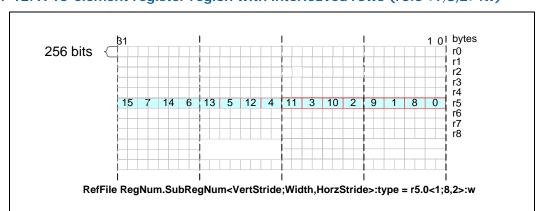

| Figure 11-12. A 16-element register region with interleaved rows (r5.0<1;8,2>:w) 320                                                                              |

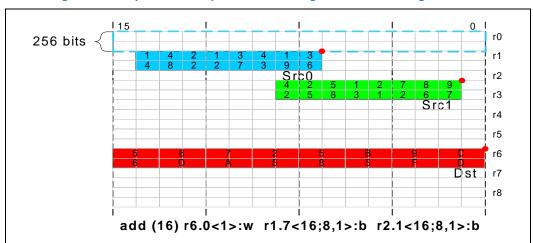

| Figure 11-13. A region description example in direct register addressing 322                                                                                      |

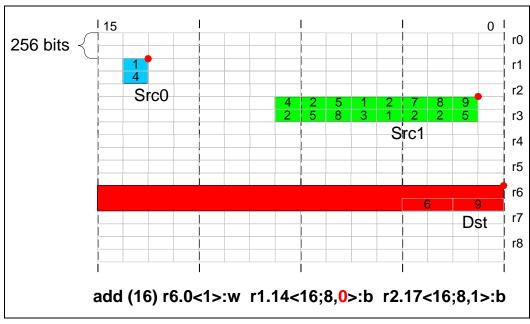

| Figure 11-14. A region description example in direct register addressing with <src0></src0>                                                                       |

| as a vector of replicated scalars                                                                                                                                 |

| Figure 11-15. An example illustrating register-indirect register addressing mode with a                                                                           |

| 1x1 index region                                                                                                                                                  |

| Figure 11-16. An example illustrating register-indirect-register addressing mode with a                                                                           |

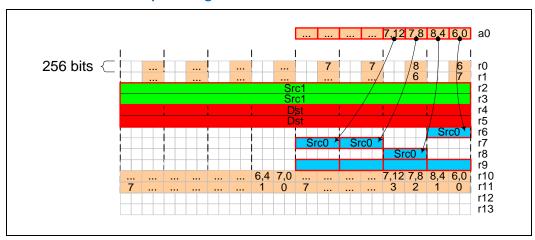

| Vx1 index region (Src0)                                                                                                                                           |

| Figure 11-17. An example illustrating register-indirect register addressing mode with a                                                                           |

| VxH index region (Src0)                                                                                                                                           |

|                                                                                                                                                                   |

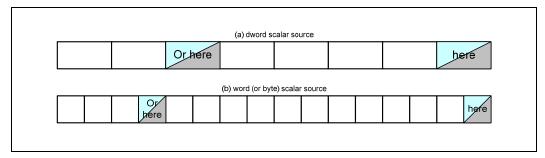

| Figure 11-19. Direct addressed vector operands in a compressed instruction 341 Figure 11-20. A packed-word operand in a dword SIMD16 compressed instruction . 342 |

|                                                                                                                                                                   |

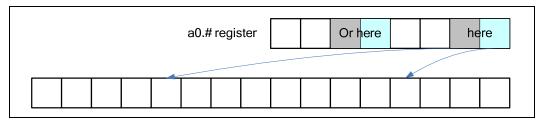

| Figure 11-21. Dword and word (or byte) scalar source in a compressed instruction. 343 Figure 11-22. Indirect-addressed source/destination operand in a compressed |

| instruction                                                                                                                                                       |

| Figure 15-1 Pivel Shader example using vector immediate 510                                                                                                       |

|                                                                                                                                                                   |

# **Tables**

| Table 1-1. Supported Chipsets                                                | 19    |

|------------------------------------------------------------------------------|-------|

| Table 2-1. Error Cases                                                       | 44    |

| Table 8-1. URB_TRANSPOSE Payload                                             |       |

| Table 8-2.URB_TRANSPOSE URB Destination Layout                               | . 250 |

| Table 10-1. Formats and ranges of numerical data types                       |       |

| Table 10-2. Example of restricted 8-bit float numbers                        |       |

| Table 10-3. Results of "Greater-Than" Comparison – CMP.G                     |       |

| Table 10-4. Results of "Less-Than" Comparison – CMP.L                        |       |

| Table 10-5. Results of "Equal-To" Comparison – CMP.E                         |       |

| Table 10-6. Results of "Not-Equal-To" Comparison – CMP.NE                    | . 267 |

| Table 10-7. Results of "Less-Than Or Equal-To" Comparison – CMP.LE           |       |

| Table 10-8. Results of "Greater-Than or Equal-To" Comparison – CMP.GE        |       |

| Table 10-9. Results of "Greater-Than" Comparison-NaN – CMPN.G                |       |

| Table 10-10. Results of "Less-Than" Comparison-NaN – CMPN.L                  |       |

| Table 10-11. Results of "Equal-To" Comparison-NaN – CMPN.E                   |       |

| Table 10-12. Results of "Not-Equal-To" Comparison-NaN – CMPN.NE              |       |

| Table 10-13. Results of "Less-Than Or Equal-To" Comparison-NaN – CMPN.LE     |       |

|                                                                              |       |

| Table 10-14. Results of "Greater-Than or Equal-To" Comparison-NaN – CMPN.GE. |       |

| Table 10-15. Supported Legacy Float Mode and Impacted Units                  |       |

| Table 10-16. Dismissed legacy behaviors                                      |       |

| Table 11-1. Summary of GRF Registers                                         |       |

| Table 11-2. GRF Registers Available in Device Hardware                       |       |

| Table 11-3. Summary of MRF Registers                                         |       |

| Table 11-4. MRF Registers Available in Device Hardware                       |       |

| Table 11-5. Summary of Architecture Registers                                |       |

| Table 11-6. Register and Subregister Numbers for Address Register            |       |

| Table 11-7. Address Register Fields                                          |       |

| Table 11-8. Register and Subregister Numbers for Accumulate Register         |       |

| Table 11-9. Accumulator Channel Precision                                    |       |

| Table 11-10. Register and Subregister Numbers for Flag Register              |       |

| Table 11-11. Flag Register Fields                                            |       |

| Table 11-12. Register and Subregister Numbers for Mask Register              |       |

| Table 11-13. Mask Register Fields                                            |       |

| Table 11-14. Register and Subregister Numbers for Mask Stack Register        | . 298 |

| Table 11-15. Mask Stack Register Fields                                      |       |

| Table 11-16. Overflow/Underflow Exception Trigger Value                      |       |

| Table 11-17. Register and Subregister Numbers for Mask Stack Depth Register  |       |

| Table 11-18. Mask Stack Depth Register Fields                                |       |

| Table 11-19. Register and Subregister Numbers for State Register             |       |

| Table 11-20. State Register Fields                                           |       |

| Table 11-21. Register and Subregister Numbers for Control Register           | . 305 |

| Table 11-22. Control Register Fields                                         | . 305 |

| Table 11-23. Register and Subregister Numbers for Notification Register      | . 312 |

| Table 11-24. Fields of Notification Register n0                              | . 313 |

| Table 11-25. Fields of Notification Register n1                              |       |

| Table 11-26. Format of the Notification Register                             | . 313 |

| Table 11-27. Register and Subregister Numbers for IP Register                |       |

| Table 11-28. IP Register Fields                                              |       |

| Table 11-29. Execution size in device hardware                                   | 330 |

|----------------------------------------------------------------------------------|-----|

| Table 11-30. Indirect source addressing support available in device hardware     | 330 |

| Table 13-1. GRF instruction execution parameters in device hardware              | 364 |

| Table 13-2. GEN4 Instruction Format                                              |     |

| Table 13-3. Definitions of Common Instruction Fields                             |     |

| Table 13-4. Definitions of Fields in Operation Doubleword (DW0)                  | 374 |

| Table 13-5. Instruction Destination Doubleword                                   |     |

| Table 13-6. Destination Register Region in Direct + Align16 mode                 | 381 |

| Table 13-7. Destination Register Region in Direct+Align1 mode                    |     |

| Table 13-8. Destination Register Region in Indirect+Align16 mode                 | 382 |

| Table 13-9. Destination Register Region in Indirect+Align1 mode                  | 382 |

| Table 13-10. Instruction Source-0 Doubleword in Direct+Align16 mode              | 383 |

| Table 13-11. Instruction Source-0 Doubleword in Direct+Align1 mode               | 384 |

| Table 13-12. Instruction Source-0 Doubleword in Indirect+Align16 mode            | 385 |

| Table 13-13. Instruction Source-0 Doubleword in Indirect+Align1 mode             | 386 |

| Table 13-14. Instruction Source-1 Doubleword in Direct + Align16 mode            | 387 |

| Table 13-15. Instruction Source-1 Doubleword in Direct + Align1 mode             | 388 |

| Table 13-16. Instruction Source-1 Doubleword in Indirect+Align16 mode            | 389 |

| Table 13-17. Instruction Source-1 Doubleword in Indirect+Align1 mode             | 390 |

| Table 13-18. GEN4 Compacted Instruction Format                                   | 391 |

| Table 13-19. Definitions of Fields in the Compact Instruction                    | 391 |

| Table 13-20. Move and Logic Instructions                                         | 394 |

| Table 13-21. Flow Control Instructions                                           | 395 |

| Table 13-22. Miscellaneous Instructions                                          | 396 |

| Table 13-23. Parallel Arithmetic Instructions                                    |     |

| Table 13-24. Vector Arithmetic Instructions                                      | 398 |

| Table 13-25. Special Instructions                                                | 399 |

| Table 14-1. Floating point addition of A (column) and B (row) in IEEE mode       | 416 |

| Table 14-2. Floating point addition of A (column) and B (row) in ALT mode        | 416 |

| Table 14-3. Floating point fraction computation in IEEE mode                     | 445 |

| Table 14-4. Floating point fraction computation in ALT mode                      | 445 |

| Table 14-5. Floating point multiplication of A (column) and B (row) in IEEE mode | 465 |

| Table 14-6. Floating point multiplication of A (column) and B (row) in ALT mode  |     |

| Table 14-7. Floating point round-down in IEEE mode                               | 475 |

| Table 14-8. Floating point round-down in ALT mode                                | 475 |

| Table 14-9. Floating point round-up in IEEE mode                                 | 477 |

| Table 14-10. Floating point round-up in ALT mode                                 |     |

| Table 14-11. Floating point round-to-even in IEEE mode                           | 479 |

| Table 14-12. Floating point round-to-even in ALT mode                            | 479 |

| Table 14-13. Floating point round-to-zero in IEEE mode                           | 481 |

| Table 14-14. Floating point round-to-zero in ALT mode                            | 481 |

| Table 14-15. Message Descriptor Definition                                       | 492 |

| Table 14-16. Sideband Signals Associated with Each Message Sent to the Shared    |     |

|                                                                                  | 493 |

# Revision History

| Document<br>Number | Revision<br>Number | Description      | Revision Date |

|--------------------|--------------------|------------------|---------------|

| 4                  | 1.0d               | Initial release. | January 2008  |

# 1 Introduction

This Programmer's Reference Manual (PRM) describes the architectural behavior and programming environment of the Intel® 965 Express Chipset family and Intel® G35 Express Chipset GMCH graphics devices (see Table 1-1). The GMCH's Graphics Controller (GC) contains an extensive set of registers and instructions for configuration, 2D, 3D, and Video systems. The PRM describes the register, instruction, and memory interfaces and the device behaviors as controlled and observed through those interfaces. The PRM also describes the registers and instructions and provides detailed bit/field descriptions.

**Note:** The term "Gen4" is used throughout the PRM to refer to the Generation 4 family of graphics devices. The devices listed in Table 1-1 are Gen4 devices.

**Table 1-1. Supported Chipsets**

| Chipset Family Name                                                                                   | Device Name                               | Device Tag |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------|------------|

| Intel <sup>®</sup> Q965 Chipset<br>Intel <sup>®</sup> Q963 Chipset<br>Intel <sup>®</sup> G965 Chipset | 82Q965 GMCH<br>82Q963 GMCH<br>82G965 GMCH | [DevBW]    |

| Intel® G35 Chipset                                                                                    | 82G35 GMCH                                | [DevBW-E]  |

| Intel® GM965 Chipset<br>Intel® GME965 Chipset                                                         | GM965 GMCH<br>GME965 GMCH                 | [DevCL]    |

#### NOTES:

- Unless otherwise specified, the information in this document applies to all of the devices mentioned in Table 1-1. For Information that does not apply to all devices, the Device Tag is used.

- 2. Throughout the PRM, references to "All" in a project field refters to all devices in Table 1-1.

- 3. Throughout the PRM, references to [DevBW] apply to both [DevBW] and [DevBW-E]. [DevBW-E] is referenced specifically for information that is [DevBW-E] only.

- Stepping info is sometimes appended to the device tag (e.g., [DevBW-C]). Information without any device tagging is applicable to all devices/steppings.

The PRM is intended for hardware, software, and firmware designers who seek to implement or use the graphic functions of the 965 Express Chipset family and G35 Express Chipset. Familiarity with 2D and 3D graphics programming is assumed.

The Programmer's Reference Manual is organized into four volumes:

#### • PRM, Volume 1: Graphics Core