# Intel<sup>®</sup> Open Source HD Graphics Programmers' Reference Manual (PRM)

# Volume 12: Display

For the 2014-2015 Intel Atom<sup>™</sup> Processors, Celeron<sup>™</sup> Processors and Pentium<sup>™</sup> Processors based on the "Cherry Trail/Braswell" Platform (Cherryview/Braswell graphics)

June 2015, Revision 1.0

# **Creative Commons License**

**You are free to Share** - to copy, distribute, display, and perform the work under the following conditions:

- **Attribution.** You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

- No Derivative Works. You may not alter, transform, or build upon this work.

# **Notices and Disclaimers**

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Implementations of the I2C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\* Other names and brands may be claimed as the property of others.

**Copyright © 2015, Intel Corporation. All rights reserved.**

# **Table of Contents**

| VGA and Extended VGA Registers               | 1  |

|----------------------------------------------|----|

| General Control and Status Registers         | 3  |

| ST00 - Input Status 0                        | 4  |

| ST01 - Input Status 1                        | 5  |

| FCR - Feature Control                        | 7  |

| MSR - Miscellaneous Output                   | 8  |

| Sequencer Registers                          | 10 |

| SRX - Sequencer Index                        | 10 |

| SR00 - Sequencer Reset                       | 10 |

| SR01 - Clocking Mode                         | 11 |

| SR02 - Plane/Map Mask                        | 13 |

| SR03 - Character Font                        | 14 |

| SR04 - Memory Mode Register                  | 16 |

| SR07 - Horizontal Character Counter Reset    | 17 |

| Graphics Controller Registers                | 18 |

| GRX - GRX Graphics Controller Index Register | 18 |

| GR00 - Set/Reset Register                    | 18 |

| GR01 - Enable Set/Reset Register             | 19 |

| GR02 - Color Compare Register                | 19 |

| GR03 - Data Rotate Register                  | 20 |

| GR04 - Read Plane Select Register            | 21 |

| GR05 - Graphics Mode Register                | 22 |

| GR06 - Miscellaneous Register                | 26 |

| GR07 - Color Don't Care Register             | 27 |

| GR08 - Bit Mask Register                     | 27 |

| Attribute Controller Registers               | 28 |

| ARX - Attribute Controller Index Register    | 28 |

| AR[00:0F] - Palette Registers [0:F]          | 29 |

| AR10 - Mode Control Register                 | 30 |

| AR11 - Overscan Color Register               | 32 |

| AR12 - Memory Plane Enable Register          | 33 |

| AR13 - Horizontal Pixel Panning Register     | 34 |

| AR14 - Color Select Register                  | 35 |

|-----------------------------------------------|----|

| VGA Color Palette Registers                   | 36 |

| DACMASK - Pixel Data Mask Register            | 37 |

| DACSTATE - DAC State Register                 | 37 |

| DACRX - Palette Read Index Register           | 38 |

| DACWX - Palette Write Index Register          | 38 |

| DACDATA - Palette Data Register               | 39 |

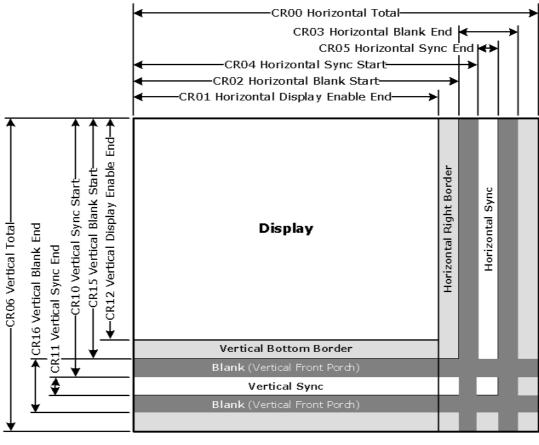

| CRT Controller Register                       | 40 |

| CRX - CRT Controller Index Register           | 41 |

| CR00 - Horizontal Total Register              | 41 |

| CR01 - Horizontal Display Enable End Register | 42 |

| CR02 - Horizontal Blanking Start Register     | 42 |

| CR03 - Horizontal Blanking End Register       | 43 |

| CR04 - Horizontal Sync Start Register         | 44 |

| CR05 - Horizontal Sync End Register           | 45 |

| CR06 - Vertical Total Register                | 46 |

| CR07 - Overflow Register (Vertical)           | 47 |

| CR08 - Preset Row Scan Register               | 49 |

| CR09 - Maximum Scan Line Register             | 50 |

| CR0A - Text Cursor Start Register             | 51 |

| CR0B - Text Cursor End Register               | 52 |

| CR0C - Start Address High Register            | 52 |

| CR0D - Start Address Low Register             | 53 |

| CR0E - Text Cursor Location High Register     | 53 |

| CR0F - Text Cursor Location Low Register      | 53 |

| CR10 - Vertical Sync Start Register           | 54 |

| CR11 - Vertical Sync End Register             | 55 |

| CR12 - Vertical Display Enable End Register   | 56 |

| CR13 - Offset Register                        | 56 |

| CR14 - Underline Location Register            | 57 |

| CR15 - Vertical Blanking Start Register       | 58 |

| CR16 - Vertical Blanking End Register         | 58 |

| CR17 - CRT Mode Control                       | 59 |

| CR18 - Line Compare Register                               | 63 |

|------------------------------------------------------------|----|

| CR22 - Memory Read Latch Data Register                     | 64 |

| CR24 - Toggle State of Attribute Controller Register       | 64 |

| Display Audio Codec Verbs                                  | 65 |

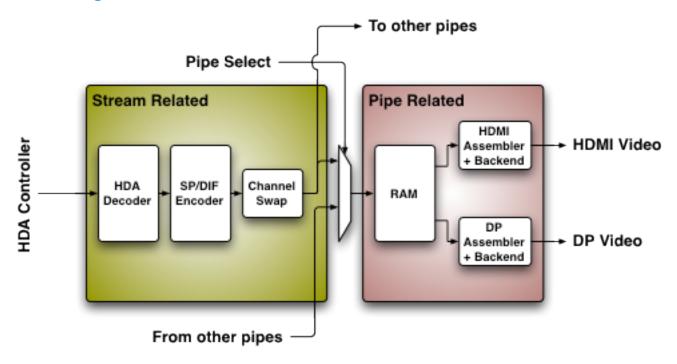

| Block Diagram                                              | 65 |

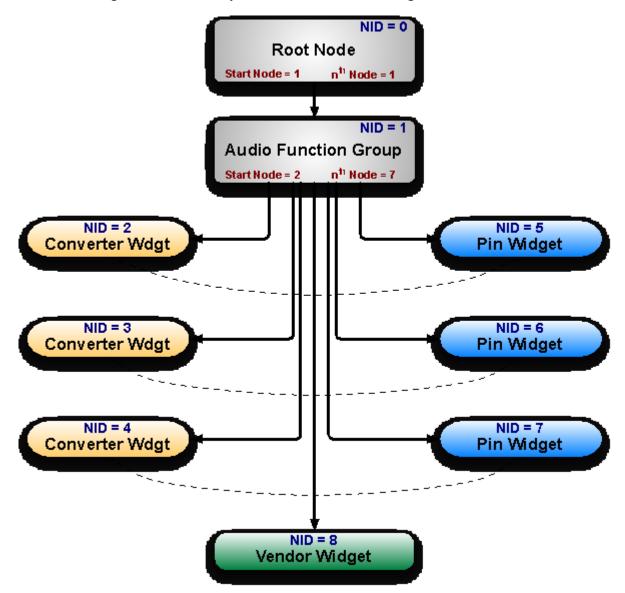

| Codec Node Hierarchy                                       | 66 |

| Programming                                                | 67 |

| Verb Support                                               | 68 |

| Parameter Support                                          | 70 |

| Node ID 00h: Root Node Verbs                               | 71 |

| F00h - Get Parameters                                      | 71 |

| Parameter 00h: VID - Vendor ID                             | 71 |

| Parameter 02h: RID - Revision ID                           | 71 |

| Parameter 04h: PARAM_SNC - Subordinate Node Count          | 71 |

| Node ID 01h: Audio Function Group Verbs                    | 72 |

| F00h: Get Parameters                                       | 72 |

| Parameter 04h: PARAM_SNC - Subordinate Node Count          | 72 |

| Parameter 05h: PARAM_FGT - Function Group Type             | 72 |

| Parameter 08h: PARAM_FGC - Function Group Capability       | 72 |

| Parameter 0Fh: PARAM_SPS - Supported Power States          | 73 |

| 705h: SET_PS - Set Power State                             | 73 |

| F05h: GET_PS - Get Power State                             | 73 |

| F20h: GET SSID - Get Subsystem ID0                         | 73 |

| 720h: SET SSID0 - Set Subsystem ID0                        | 73 |

| 721h: SET SSID1 - Set Subsystem ID1                        | 74 |

| 722h: SET SSID2 - Set Subsystem ID2                        | 74 |

| 723h: SET SSID3 - Set Subsystem ID3                        | 74 |

| Node ID 02h, 03h, 04h: Audio Output Convertor Widget Verbs | 75 |

| 2h/Ah: SET/GET_SDF - Set/GET Stream Descriptor Format      | 75 |

| F00h: Get Parameters                                       | 76 |

| Parameter 09h: AWC - Audio Widget Capabilities             | 76 |

| Parameter 0Ah: PSB - PCM Sizes and Bit Rates               | 76 |

| Parameter 0Bh: SF - Stream Formats                         | 77 |

| Parameter 0Fh: PARAM_SPS - Supported Power States          | 77 |

|------------------------------------------------------------|----|

| 705h: SET_PS - Set Power State                             | 77 |

| F05h: GET_PS - Get Power State                             | 78 |

| 706h/F06h: GET/SET_CSID - Get/Set Channel and Stream ID    | 78 |

| Digital Converter Verbs                                    | 78 |

| F0Dh: GET_DC - Get Digital Converter                       | 78 |

| 70Dh: SET_DC1 - Set Digital Converter 1                    | 79 |

| 70Eh: Digital Converter 2                                  | 79 |

| 73Eh: Digital Converter 3                                  | 79 |

| 73Fh: Digital Converter 4                                  | 79 |

| 72Dh/F2Dh: GET/SET_CCC - Get/Set Converter Channel Count   | 79 |

| Node ID 05h, 06h, 07h: Pin Widget Verbs                    | 80 |

| 3h: SET_AM - Set Amplifier Mute                            | 80 |

| B8h: GET_AM - Get Amplifier Mute                           | 81 |

| F00h: Get Parameters                                       | 81 |

| Parameter 09h: AWC - Audio Widget Capabilities             | 81 |

| Parameter 0Ch: PC - Pin Capabilities                       | 82 |

| Parameter 0Eh: CLL - Connection List Length                | 82 |

| Parameter 12h: OAC - Output Amplifier Capabilities         | 82 |

| Parameter 15h: DLL - Device List Length                    | 82 |

| Parameter 0Fh: PARAM_SPS - Supported Power States          | 83 |

| 701h/F01h: SET/GET_CSC - Set/Get Connection Select Control | 83 |

| F02h: GET_CLE - Get Connection List Entry                  | 83 |

| 705h: SET_PS - Set Power State                             | 83 |

| F05h: GET_PS - Get Power State                             | 83 |

| 707h/F07h: SET/GET_PWC - Set/Get Pin Widget Control        | 84 |

| 708h/F08h: SET/GET_UE - Set/Get Unsolicited Enable         | 84 |

| F09h: GET_PS - Get Pin Sense                               | 84 |

| 71Ch: SET_CD0 - Set Configuration Default Byte 0           | 84 |

| 71Dh: SET_CD1 - Set Configuration Default Byte 1           | 84 |

| 71Eh: SET_CD2 - Set Configuration Default Byte 2           | 84 |

| 71Fh: SET_CD3 - Set Configuration Default Byte 3           | 85 |

| F1Ch: GET_CD - Get Configuration Default                   | 85 |

|   | F2Eh: HDMI/DP Info Size                                      | 85 |

|---|--------------------------------------------------------------|----|

|   | F2Fh: Get ELD Data                                           | 86 |

|   | Parameter nn: ELD Data                                       | 86 |

|   | 730h/F30h: SET/GET_HII - Set/Get HDMI Info Index             | 86 |

|   | 731h/F31h: SET/GET_HID - Set/Get HDMI Info Data              | 86 |

|   | 732h/F32h: SET/GET_HITC - Set/Get HDMI Info Transmit Control | 86 |

|   | 733h SET_PC - Set Protection Control                         | 87 |

|   | 734h/F34h: SET/GET_CCM - Get/Set Converter Channel Map       | 87 |

|   | 735h: SET_DS - Set Device Select                             | 87 |

|   | F35h: GET_DS - Get Device Select                             | 87 |

|   | F36h: GET_DDLE - Get Display Device List Entry               | 88 |

|   | 73Ch/F3Ch: SET/GET_DPID - Set/Get DisplayPort Stream ID      | 88 |

| N | ode ID 08h: Intel Vendor Widget Verbs                        | 89 |

|   | F00h: Get Parameters                                         | 89 |

|   | Parameter 09h: AWC - Audio Widget Capabilities               | 89 |

|   | 781h/F81h: GET/SET_VV - Get/Set HDMI Vendor Verb             | 89 |

|   | F83h: GET_CGTC - Get Captured GTC Value                      | 90 |

|   | F84h: GET_CWC - Get Captured Wall Clock Value                | 90 |

|   | F85h: GET GOF - Get GTC Offset Value                         | 90 |

|   | 785h: SET GOF0 - Set GTC Offset Value Byte 0                 | 90 |

|   | 786h: SET GOF1 - Set GTC Offset Value Byte 1                 | 90 |

|   | 787h: SET GOF2 - Set GTC Offset Value Byte 2                 | 90 |

|   | 788h: SET GOF3 - GTC Offset Value Byte 3                     | 90 |

|   | 789h/F89h: SET/GET_GDI - Set/Get GTC Device Index            | 90 |

# **VGA and Extended VGA Registers**

This section describes the registers and the functional operation notations for the observable registers in the VGA section. This functionality is provided as a means for support of legacy applications and operating systems. It is important to note that these registers in general have the desired effects only when running VGA display modes.

The main exceptions to this are the palette interface which allows real mode DOS applications and full screen VGA applications under an OS control running in high resolution (non-VGA) modes to access the palette through the VGA register mechanisms and the use of the ST01 status bits that determine when the VGA enters display enable and sync periods. Other exceptions include the register bits that control the memory accesses through the A000:0000 and B000:0000 memory segments which are used during operating system emulation of VGA for "DOS box" applications. Some of the functions of the VGA are enabled or defeated through the programming of the VGA control register bits that are located in the MMIO register space.

Given the legacy nature of this function, it has been adapted to the changing environment that it must operate within. The three most notable changes are the addition of high resolution display mode support, new operating system support, and the use of fixed resolution display devices (such as LCD panels). Additional control bits in the PCI Config space will affect the ability to access the registers and memory aperture associated with VGA.

| Mode of Operation | VGA<br>Disable | VGA<br>Display | VGA Registers | Palette (VGA) | VGA<br>Memory | VGA Banking |

|-------------------|----------------|----------------|---------------|---------------|---------------|-------------|

| VGA DOS           | No             | Yes            | Yes           | Yes           | Yes           | No          |

| HiRes DOS         | Yes            | No             | Yes           | Yes           | No            | Yes         |

| Fullscreen DOS    | Yes/No         | No/Yes         | Yes           | Yes           | Yes           | Yes         |

| DOS Emulation     | Yes            | No             | Yes           | Yes           | Yes           | Yes         |

| VGA Display<br>Mode  | Dot Clock Select                 | Dot Clock<br>Range  | 132<br>Column<br>Text<br>Support | 9-Dot<br>Disable<br>Support | Main<br>Use                |

|----------------------|----------------------------------|---------------------|----------------------------------|-----------------------------|----------------------------|

| Native               | VGA Clock Select                 | 25/28 MHz           | No                               | No                          | Analog CRT (VGA connector) |

| Centered             | Fixed at display<br>Requirements | Product<br>Specific | No                               | Yes                         | Digital Display            |

| Upper Left<br>Corner | Fixed at display<br>Requirements | Product<br>Specific | No                               | Yes                         | Internal Panel             |

Native, Centered, and Upper Left Corner support varies from product to product.

Even in the native VGA display operational modes, not all combinations of bit settings result in functional operating modes. VGA display modes have the restriction that they can be used only when all other display planes are disabled.

These registers are accessed via I/O space. The I/O space resides in the PCI compatibility hole and uses only the addresses that were part of the original VGA I/O space (which includes EGA and MDA emulation). Accesses to the VGA I/O addresses are steered to the proper bus and rely on proper setup of bridge registers. Extended VGA registers such as GR10 and GR11 use additional indexes for the already defined I/O addresses. VGA register accesses are allowed as 8 or 16 bit naturally aligned transactions only. Word transactions must have the least significant bit of the address set to zero. DWORD I/O operations should not be performed on these registers.

Some products may support access to these registers through MMIO. The access method varies and is documented elsewhere.

# **General Control and Status Registers**

The setup, enable, and general registers are all directly accessible by the CPU. A sub indexing scheme is not used to read from and write to these registers.

|      |                                   | Read       |                        | Write      |                      |

|------|-----------------------------------|------------|------------------------|------------|----------------------|

| Name | Function                          | I/O        | Memory Offset          | I/O        | <b>Memory Offset</b> |

| ST00 | VGA Input Status Register 0       | 3C2h       | 3C2h                   |            |                      |

| ST01 | VGA Input Status Register 1       | 3BAh/3DAh1 | 3BAh/3DAh <sup>1</sup> |            |                      |

| FCR  | VGA Feature Control Register      | 3CAh       | 3CAh                   | 3BAh/3DAh1 | 3BAh/3DAh1           |

| MSR  | VGA Miscellaneous Output Register | 3CCh       | 3CCh                   | 3C2h       | 3C2h                 |

<sup>1</sup> The address selection for ST01 reads and FCR writes is dependent on CGA or MDA emulation mode as selected via the MSR register.

Various bits in these registers provide control over the real-time status of the horizontal sync signal, the horizontal retrace interval, the vertical sync signal, and the vertical retrace interval. The horizontal retrace interval is the period during the drawing of each scan line containing active video data, when the active video data is not being displayed. This period includes the horizontal front and back porches, and the horizontal sync pulse. The horizontal retrace interval is always longer than the horizontal sync pulse. The vertical retrace interval is the period during which the scan lines not containing active video data are drawn. This includes the vertical front porch, back porch, and the vertical sync pulse. The vertical is normally longer than the vertical sync pulse.

#### ST00 - Input Status 0

# I/O (and Memory Offset) Address: 3C2h

Default:

#### Attributes:

Read Only

00h

| Bit | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | <b>CRT Interrupt Pending.</b> This bit is here for EGA compatibility and <b>will always return zero</b> . The generation of interrupts was originally enabled, through bits [4,5] of the Vertical Retrace End Register (CR11). This ability to generate interrupts at the start of the vertical retrace interval is a feature that is typically unused by DOS software and therefore is only supported through other means for use under a operating system support. |  |  |  |

|     | 0 = CRT (vertical retrace interval) interrupt is not pending.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|     | 1 = CRT (vertical retrace interval) interrupt is pending                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 6:5 | Reserved. Read as 0s.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 4   | <b>RGB Comparator / Sense.</b> This bit is here for compatibility and <b>will always</b><br><b>return one</b> . Monitor detection must be done be done through the programming<br>of registers in the MMIO space.                                                                                                                                                                                                                                                    |  |  |  |

|     | 0 = Below threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|     | 1 = Above threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 3:0 | Reserved. Read as 0s.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

# ST01 - Input Status 1

# I/O (and Memory Offset) Address:3BAh/3DAhDefault:00h

#### Attributes:

Read Only

The address selection is dependent on CGA or MDA emulation mode as selected via the MSR register.

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Reserved (as per VGA specification). Read as 0s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Reserved. Read as 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5:4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>Video Feedback 1, 0.</b> These bits are connected to 2 of the 8 color bits sent to the palette. Bits 4 and 5 of the Color Plane Enable Register (AR12) selects which two of the 8 possible color bits become connected to these 2 bits of this register. These bits exist for EGA compatibility.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Vertical Retrace/Video.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 = VSYNC inactive (Indicates that a vertical retrace interval is not taking place).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 = VSYNC active (Indicates that a vertical retrace interval is taking place).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VGA pixel generation is not locked to the display output but is loosely<br>A VSYNC indication may not occur during the actual VSYNC going to t<br>display but during the VSYNC that is generated as part of the VGA pixe<br>generation. The exact relationship will vary with the VGA display opera<br>mode. This status bit will remain active when the VGA is disabled and t<br>device is running in high resolution modes (non-VGA) to allow for app<br>that (now incorrectly) use these status registers bits. In this case, the st<br>come from the pipe that the VGA is assigned to. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bits 4 and 5 of the Vertical Retrace End Register (CR11) previously could<br>program this bit to generate an interrupt at the start of the vertical retrace<br>interval. This ability to generate interrupts at the start of the vertical retrace<br>interval is a feature that is largely unused by legacy software. Interrupts are not<br>supported through the VGA register bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2:1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Reserved. Read as 0s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>Display Enable Output.</b> Display Enable is a status bit (bit 0) in VGA Input<br>Status Register 1 that indicates when either a horizontal retrace interval or a<br>vertical retrace interval is taking place. This bit was used with the EGA graphics<br>system (and the ones that preceded it, including MDA and CGA). In those<br>cases, it was important to check the status of this bit to ensure that one or the<br>other retrace intervals was taking place before reading from or writing to the<br>frame buffer. In these earlier systems, reading from or writing to the frame<br>buffer at times outside the retrace intervals meant that the CRT controller<br>would be denied access to the frame buffer. Those behaviors resulted in either<br>"snow" or a flickering display. This bit provides compatibility with software |

| Bit                                                                                                                                                                                                                                      | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| designed for those early graphics controllers. This bit is currently use<br>applications that access the palette to prevent the sparkle associated<br>and write accesses to the palette RAM with the same address on the<br>clock cycle. |                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                                                                                                                                                                                                          | This status bit remains active when the VGA display is disabled and the device is running in high resolution modes (non-VGA) to allow for applications that (now considered incorrect) use these status registers bits. In this case, the status will come from the pipe that the VGA is assigned to. When in panel fitting VGA or centered VGA operation, the meaning of these bits will not be consistent with native VGA timings. |  |  |

| 0 = Active display data is being sent to the display. Neither a horizontal reinterval or a vertical retrace interval is currently taking place.                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                                                                                                                                                                                                          | 1 = Either a horizontal retrace interval (horizontal blanking) or a vertical retrace interval (vertical blanking) is currently taking place.                                                                                                                                                                                                                                                                                         |  |  |

## FCR - Feature Control

#### I/O (and Memory Offset) Address: 3BAh/3DAh - Write; 3CAh - Read

| Default: | 00h  |

|----------|------|

| Deradit. | 0011 |

#### Attributes: See Address above

The I/O address used for writes is dependent on CGA or MDA emulation mode as selected via the MSR register. In the original EGA, bits 0 and 1 were used as part of the feature connector interface. Feature connector is not supported in these devices and those bits will always read as zero.

| Bit                                                                                                                                                                                                                                               | Descriptions                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4                                                                                                                                                                                                                                               | Reserved. Read as 0.                                                                                                                        |

| <sup>3</sup> <b>VSYNC Control.</b> This bit is provided for compatibility only and has function. Reads and writes to this bit have no effect other than to cl value of this bit. The previous definition of this bit selected the outp VSYNC pin. |                                                                                                                                             |

|                                                                                                                                                                                                                                                   | 0 = Was used to set VSYNC output on the VSYNC pin (default).                                                                                |

|                                                                                                                                                                                                                                                   | 1 = Was used to set the logical 'OR' of VSYNC and Display Enable output on<br>the VSYNC pin. This capability was not typically very useful. |

| 2:0                                                                                                                                                                                                                                               | Reserved. Read as 0.                                                                                                                        |

#### **MSR - Miscellaneous Output**

# I/O (and Memory Offset) Address: 3C2h - Write; 3CCh - Read

Default:

00h

#### Attributes:

See Address above

| Bit | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | <b>CRT VSYNC Polarity.</b> This is a legacy function that is used in native VGA modes. For most cases, sync polarity will be controlled by the port control bits. The VGA settings can be optionally selected for compatibility with the original VGA when used in the VGA native mode. Sync polarity was used in VGA to signal the monitor how many lines of active display are being generated.                         |

|     | 0 = Positive Polarity (default).                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 1 = Negative Polarity.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6   | <b>CRT HSYNC Polarity.</b> This is a legacy function that is used in native VGA modes. For most cases, sync polarity will be controlled by the port control bits. The VGA settings can be optionally selected for compatibility with the original VGA when used in the VGA native mode.                                                                                                                                   |

|     | 0 = Positive Polarity (default).                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 1 = Negative Polarity                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5   | <b>Page Select.</b> In Odd/Even Memory Map Mode 1 (GR6), this bit selects the upper or lower 64 KB page in display memory for CPU access:                                                                                                                                                                                                                                                                                 |

|     | 0 = Upper page (default)                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 1 = Lower page.                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | Selects between two 64KB pages of frame buffer memory during standard VGA odd/even modes (modes 0h through 5h). Bit 1 of register GR06 can also program this bit in other modes. This bit is would normally set to 1 by the software.                                                                                                                                                                                     |

| 4   | Reserved. Read as 0.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3:2 | <b>Clock Select.</b> These bits can select the dot clock source for the CRT interface. The bits should be used to select the dot clock in standard native VGA modes only. When in the centering or upper left corner modes, these bits should be set to have no effect on the clock rate. The actual frequencies that these bits select, if they have any affect at all, is programmable through the DPLL MMIO registers. |

|     | 00 = CLK0, 25.175 MHz (for standard VGA modes with 640 pixel (8-dot) horizontal resolution) (default)                                                                                                                                                                                                                                                                                                                     |

|     | 01 = CLK1, 28.322 MHz. (for standard VGA modes with 720 pixel (9-dot) horizontal resolution)                                                                                                                                                                                                                                                                                                                              |

|     | 10 = Was used to select an external clock (now unused)                                                                                                                                                                                                                                                                                                                                                                    |

|     | 11 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1   | <b>A0000-BFFFFh Memory Access Enable.</b> VGA Compatibility bit enables access to video memory (frame buffer) at A0000-BFFFFh. When disabled, accesses to VGA memory are blocked in this region. This bit is independent of and does not block CPU access to the video linear frame buffer at other addresses.                                                                                                            |

| Bit | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 0 = Prevent CPU access to memory/registers/ROM through the A0000-BFFFF VGA memory aperture (default).<br>1 = Allow CPU access to memory/registers/ROM through the A0000-BFFFF VGA memory aperture. Delete?                                                                                                                                                                                                                                                              |

| 0   | <b>I/O Address Select.</b> This bit selects 3Bxh or 3Dxh as the I/O address for the CRT Controller registers, the Feature Control Register (FCR), and Input Status Register 1 (ST01). Presently ignored (whole range is claimed), but will "ignore" 3Bx for color configuration or 3Dx for monochrome.<br>It is typical in AGP chipsets to shadow this bit and properly steer I/O cycles to the proper bus for operation where a MDA exists on another bus such as ISA. |

|     | 0 = Select 3Bxh I/O address (MDA emulation) (default).<br>1 = Select 3Dxh I/O address (CGA emulation).                                                                                                                                                                                                                                                                                                                                                                  |

In standard VGA modes using the analog VGA connector, bits 7 and 6 indicate which of the three standard VGA vertical resolutions the standard VGA display should use. Extended modes, including those with a vertical resolution of 480 scan lines, may use a setting of 0 for both of these bits. Different connector standards and timing standards specify the proper use of sync polarity. This setting was "reserved" in the VGA standard.

#### **Analog CRT Display Sync Polarities**

| V | Η | Display  | Horizontal Frequency | Vertical Frequency |

|---|---|----------|----------------------|--------------------|

| Ρ | Ρ | 200 Line | 15.7 KHz             | 60 Hz              |

| Ν | Ρ | 350 Line | 21.8 KHz             | 60 Hz              |

| Ρ | Ζ | 400 Line | 31.5 KHz             | 70 Hz              |

| Ν | Ν | 480 Line | 31.5 KHz             | 60 Hz              |

#### **Sequencer Registers**

The sequencer registers are accessed via either I/O space or Memory space. To access registers the VGA Sequencer Index register (SRX) at I/O address 3C4h (or memory address 3C4h) is written with the index of the desired register. Then the desired register is accessed through the data port for the sequencer registers at I/O address 3C5 (or memory address 3C5).

#### **SRX - Sequencer Index**

| I/O (and Memory Offset) Address: 3C4h |            |  |

|---------------------------------------|------------|--|

| Default:                              | 00h        |  |

| Attributes:                           | Read/Write |  |

| Bit | Description                                                                                                                               |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | Reserved. Read as 0s.                                                                                                                     |

| 2:0 | <b>Sequencer Index.</b> This field contains a 3-bit Sequencer Index value used to access sequencer data registers at indices 0 through 7. |

#### **SR00 - Sequencer Reset**

| I/O (and Memory Offset) A | Address: 3C5h(Index=00h) |

|---------------------------|--------------------------|

|---------------------------|--------------------------|

00h

#### Attributes:

Read/Write

| Bit | Descriptions                                          |

|-----|-------------------------------------------------------|

| 7:2 | Reserved. Read as 0.                                  |

| 1   | Reserved. Reserved for VGA compatibility (was reset). |

| 0   | Reserved. Reserved for VGA compatibility. (was reset) |

# SR01 - Clocking Mode

# I/O (and Memory Offset) Address: 3C5h (Index=01h)Default: 00hAttributes: Read/Write

| Bit | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:6 | Reserved. Read as 0s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 5   | Screen Off.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|     | 0 = Normal Operation (default).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|     | 1 = Disables video output (blanks the screen) and turns off display data fetches.<br>Synchronization pulses to the display, however, are maintained. Setting this bit to<br>1 had been used as a way to more rapidly update and improve CPU access<br>performance to the frame buffer during VGA modes. In non-VGA modes (VGA<br>Disable=1), this bit has no effect. Before the VGA is disabled through the MMIO<br>VGA control register, this bit should be set to stop the memory accesses from the<br>display. |  |

|     | The following sequence must be used when disabling the VGA plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|     | 1. Write SR01 to set bit 5 = 1 to disable video output.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|     | 2. Wait for 100us.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|     | <ol> <li>Disable the VGA plane via Bit 31 of the MMIO VGA control register<br/>(location found in the MMIO display register programming specification).</li> </ol>                                                                                                                                                                                                                                                                                                                                                |  |

| 4   | Shift 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|     | 0 = Load video shift registers every 1 or 2 character clocks (depending on bit 2 of this register) (default).                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|     | 1 = Load shift registers every 4th character clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 3   | <b>Dot Clock Divide.</b> Setting this bit to 1 stretches doubles all horizontal timing periods that are specified in the VGA horizontal CRTC registers. This bit is used in standard VGA 40-column text modes to stretch timings to create horizontal resolutions of either 320 or 360 pixels (as opposed to 640 or 720 pixels, normally used in standard VGA 80-column text modes). The effect of this is that there will actually be twice the number of pixels sent to the display per line.                   |  |

|     | 0 = Pixel clock is left unaltered (used for 640 (720) pixel modes); (default).                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|     | 1 = Pixel clock divided by 2 (used for 320 (360) pixel modes).                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 2   | Shift Load. Bit 4 of this register must be 0 for this bit to be effective.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|     | 0 = Load video data shift registers every character clock (default).                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Bit | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 1 = Load video data shift registers every other character clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1   | Reserved. Read as 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0   | <b>8/9 Dot Clocks.</b> This bit determines whether a character clock is 8 or 9 dot clocks long if clock doubling is disabled and 16 or 18 clocks if it is. This also changes the interpretation of the pixel panning values (see chart). An additional control bit determines if this bit is to be ignored and 8-dot characters are to be used always. The 9-dot disable would be used when doubling the horizontal pixels on a 1280 wide display or non-doubling on a 640 wide display. Panning however will occur according to the expected outcome. |

|     | 0 = 9 dot clocks (9 horizontal pixels) per character in text modes with a horizontal resolution of 720 pixels.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 1 = 8 dot clocks (8 horizontal pixels) per character in text or graphics modes with a horizontal resolution of 640 pixels.                                                                                                                                                                                                                                                                                                                                                                                                                             |

# SR02 - Plane/Map Mask

# I/O (and Memory Offset) Address: 3C5h (Index=02h)

Default:

00h

#### Attributes:

Read/Write

| Bit | Descriptions                                                                                                                                                                |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Reserved. Read as 0s.                                                                                                                                                       |

| 3:0 | <b>Memory Planes [3:0] Processor Write Access Enable.</b> In both the Odd/Even Mode and the Chain 4 Mode, these bits still control access to the corresponding color plane. |

|     | 0 = Disable.                                                                                                                                                                |

|     | 1 = Enable.                                                                                                                                                                 |

|     | This register is referred to in the VGA standard as the Map Mask Register.                                                                                                  |

#### SR03 - Character Font

#### I/O (and Memory Offset) Address: 3C5h (index=03h)

| Default:    | 00h        |

|-------------|------------|

| Attributes: | Read/Write |

In text modes, bit 3 of the video data's attribute byte normally controls the foreground intensity. This bit may be redefined to control switching between character sets. This latter function is enabled whenever there is a difference in the values of the Character Font Select A and the Character Font Select B bits. If the two values are the same, the character select function is disabled and attribute bit 3 controls the foreground intensity.

Bit 1 of the Memory Mode Register (SR04) must be set to 1 for the character font select function of this register to be active. Otherwise, only character maps 0 and 4 are available.

| Bit                                                                                                                                                                                               |                                | Descriptions                                                                                                                                                                                                                            |                                             |  |