# Intel® HD Graphics OpenSource PRM

Volume 1 Part 1: Graphics Core

For the all new 2010 Intel Core Processor Family Programmer's Reference Manual (PRM)

February 2010

Revision 1.0

#### You are free:

to Share -- to copy, distribute, display, and perform the work

#### Under the following conditions:

**Attribution**. You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

No Derivative Works. You may not alter, transform, or build upon this work.

You are not obligated to provide Intel with comments or suggestions regarding this document. However, should you provide Intel with comments or suggestions for the modification, correction, improvement, or enhancement of: 9a) this document; or (b) Intel products, which may embody this document, you grant to Intel a non-exclusive, irrevocable, worldwide, royalty-free license, with the right to sublicense Intel's licensees and customers, under Recipient intellectual property rights, to use and disclose such comments and suggestions in any manner Intel chooses and to display, perform, copy, make, have made, use, sell, and otherwise dispose of Intel's and its sublicensee's products embodying such comments and suggestions in any manner and via any media Intel chooses, without reference to the source.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Sandy Bridge chipset family, Havendale/Auburndale chipset family, Intel® 965 Express Chipset Family, Intel® G35 Express Chipset, and Intel® 965GMx Chipset Mobile Family Graphics Controller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

I2C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I2C bus/protocol and was developed by Intel. Implementations of the I2C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and the Intel are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2010, Intel Corporation. All rights reserved.

# **Contents**

| 1.  | Introduction                                         |    |

|-----|------------------------------------------------------|----|

| 1.1 | Reserved Bits and Software Compatibility             | 9  |

| 1.2 | Terminology                                          | 9  |

| 2.  | Graphics Device Overview                             | 18 |

| 2.1 | Graphics Memory Controller Hub (GMCH)                |    |

| 2.2 |                                                      |    |

| 3.  | Graphics Processing Engine (GPE)                     | 21 |

| 3.1 |                                                      | 21 |

| 3.2 |                                                      |    |

| 3.  | .2.1 Block Diagram                                   |    |

| 3.  | .2.2 Command Stream (CS) Unit                        | 23 |

|     | .2.3 3D Pipeline                                     |    |

|     | .2.4 Media Pipeline                                  |    |

|     | .2.5 GENX Subsystem                                  |    |

|     | .2.6 GPE Function IDs                                |    |

| 3.3 |                                                      |    |

| 3.4 |                                                      |    |

|     | .4.1 URB_FENCE Constant URB Entries (CURBEs)         |    |

|     | .5.1 Overview                                        |    |

| _   | .5.2 Multiple CURBE Allocation                       |    |

|     | .5.3 CS URB STATE                                    |    |

|     | .5.4 CONSTANT BUFFER                                 |    |

|     | .5.5 MEMORY OBJECT CONTROL STATE                     |    |

| 3.6 |                                                      |    |

| 3.  | .6.1 STÁTE_BASE_ADDRESS                              | 40 |

| 3.7 |                                                      | 47 |

|     | .7.1 STATE_POINTER_INVALIDATE ([DevCTG+])            |    |

| 3.8 |                                                      |    |

|     | .8.1 STATE_PREFETCH                                  |    |

| 3.9 | - 7 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1              |    |

| _   | .9.1 STATE_SIP                                       |    |

|     | 0 Command Ordering Rules                             |    |

| -   | .10.1 PIPELINE_SELECT                                |    |

|     | .10.3 URB-Related State-Setting Commands             |    |

|     | .10.4 Common Pipeline State-Setting Commands         |    |

|     | .10.5 3D Pipeline-Specific State-Setting Commands    |    |

| _   | .10.6 Media Pipeline-Specific State-Setting Commands |    |

|     | .10.7 URB_FENCE (URB Fencing & Entry Allocation)     |    |

| 3.  | .10.8 CONSTANT_BUFFER (CURBE Load)                   |    |

| 3.  | .10.9 3DPRIMITIVE                                    |    |

| 3.  | .10.10 MEDIA_OBJECT                                  | 56 |

| 4.  | Video Codec Engine                                   | 57 |

| 4.1 | Video Command Streamer (VCS)                         |    |

| 4.2 | CRYPTO Engine                                        | 59 |

| 4   | .2.1 MFX CRYPTO COPY BASE ADDR Command               | 60 |

| 4.2.2          | MFX_CRYPTO_KEY_EXCHANGE State command            | 61           |

|----------------|--------------------------------------------------|--------------|

| 4.2.3          | MFX_CRYPTO_COPY Object Command                   | 62           |

| 4.2.4          | Crypto MMIO Register Read-Only Commands          | 64           |

| 5. Gra         | phics Command Formats                            | C E          |

|                | ommand Formats                                   |              |

| 5.1.1          | Memory Interface Commands                        |              |

| 5.1.1          | 2D Commands                                      |              |

| 5.1.2          | 3D/Media Commands                                |              |

|                | Video Codec Commands                             |              |

| 5.1.4<br>5.1.5 | Command Header                                   |              |

|                |                                                  |              |

|                | ommand Map                                       |              |

| 5.2.1          | Memory Interface Command Map                     |              |

| 5.2.2          | 2D Command Map                                   |              |

| 5.2.3          | 3D/Media Command Map                             |              |

| 5.2.4          | Video Codec Command Map                          | /6           |

| 6. Reg         | ister Address Maps                               | 81           |

|                | raphics Register Address Map                     |              |

| 6.1.1          | Memory and I/O Space Registers                   |              |

| 6.1.2          |                                                  |              |

| 6.1.3          |                                                  |              |

|                | GA and Extended VGA Register Map                 |              |

|                | VGA and Extended VGA I/O and Memory Register Map |              |

|                | direct VGA and Extended VGA Register Indices     |              |

|                | <u> </u>                                         |              |

|                | nory Data Formats                                |              |

|                | emory Object Overview                            |              |

| 7.1.1          | Memory Object Types                              |              |

|                | hannel Formats                                   |              |

| 7.2.1          | Unsigned Normalized (UNORM)                      |              |

| 7.2.2          | Gamma Conversion (SRGB)                          |              |

| 7.2.3          | Signed Normalized (SNORM)                        |              |

| 7.2.4          | Unsigned Integer (UINT/USCALED)                  |              |

| 7.2.5          | Signed Integer (SINT/SSCALED)                    |              |

| 7.2.6          | Floating Point (FLOAT)                           |              |

| 7.3 No         | on-Video Surface Formats                         | 93           |

| 7.3.1          | Surface Format Naming                            | 94           |

| 7.3.2          | Intensity Formats                                | 94           |

| 7.3.3          | Luminance Formats                                | 94           |

| 7.3.4          | R1_UNORM (same as R1_UINT) and MONO8             | 94           |

| 7.3.5          | Palette Formats                                  | 95           |

| 7.4 C          | ompressed Surface Formats                        |              |

| 7.4.1          | FXT Texture Formats                              | 98           |

| 7.4.2          | BC4                                              | 112          |

| 7.4.3          | BC5                                              |              |

| 7.5 Vi         | deo Pixel/Texel Formats                          |              |

| 7.5.1          | Packed Memory Organization                       |              |

| 7.5.2          | Planar Memory Organization                       |              |

|                | urface Memory Organizations                      |              |

|                | raphics Translation Tables                       |              |

|                | ardware Status Page                              |              |

|                | struction Ring Buffers                           |              |

|                | nstruction Batch Buffers                         |              |

|                | Display, Overlay, Cursor Surfaces                |              |

| 7.11 L         | /iopiay, Ovoliay, Ouloul Ouliauto                | 1 <b>∠</b> U |

|      | 2D Render Surfaces                            |     |

|------|-----------------------------------------------|-----|

| 7.13 | 2D Monochrome Source                          | 120 |

| 7.14 | 2D Color Pattern                              | 120 |

|      |                                               |     |

| 7.16 | 3D Depth Buffer Surfaces                      | 121 |

| 7.17 | 3D Separate Stencil Buffer Surfaces [DEVILK+] | 121 |

| 7.18 | Surface Layout                                | 122 |

| 7.18 | 8.1 Buffers                                   |     |

| 7.18 | 8.2 1D Surfaces                               | 123 |

| 7.18 | 8.3 2D Surfaces                               | 123 |

|      | 8.4 Cube Surfaces                             |     |

| 7.18 | 8.5 3D Surfaces                               | 130 |

| 7.19 | Surface Padding Requirements                  | 131 |

| 7.19 | 9.1 Sampling Engine Surfaces                  | 131 |

|      | 9.2 Render Target and Media Surfaces          |     |

| Document Number       | <b>Revision Number</b> | Description    | <b>Revision Date</b> |

|-----------------------|------------------------|----------------|----------------------|

| IHD-OS-022810-R1V1PT1 | 10                     | First Release. | February 2010        |

# 1. Introduction

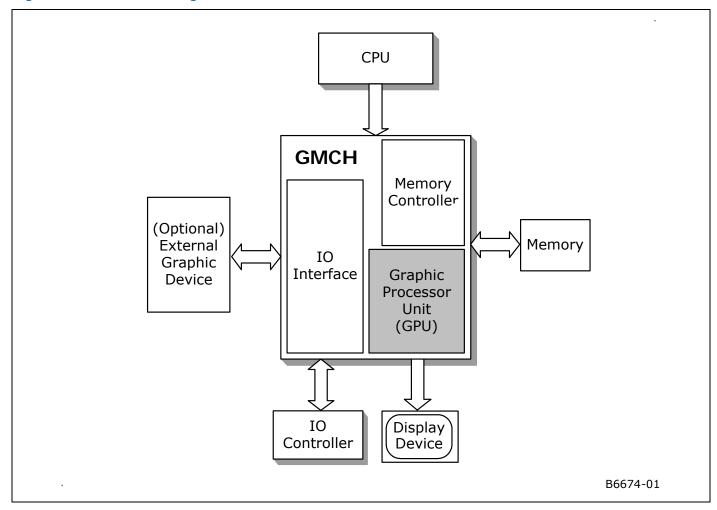

The Intel® HD Graphics Open Source (PRM) describes the architectural behavior and programming environment of the Havendale/Auburndale chipset family. The Graphics Controller (GC) contains an extensive set of registers and instructions for configuration, 2D, 3D, and Video systems. The PRM describes the register, instruction, and memory interfaces and the device behaviors as controlled and observed through those interfaces. The PRM also describes the registers and instructions and provides detailed bit/field descriptions.

The Programmer's Reference Manual is organized into four volumes:

### PRM, Volume 1: Graphics Core

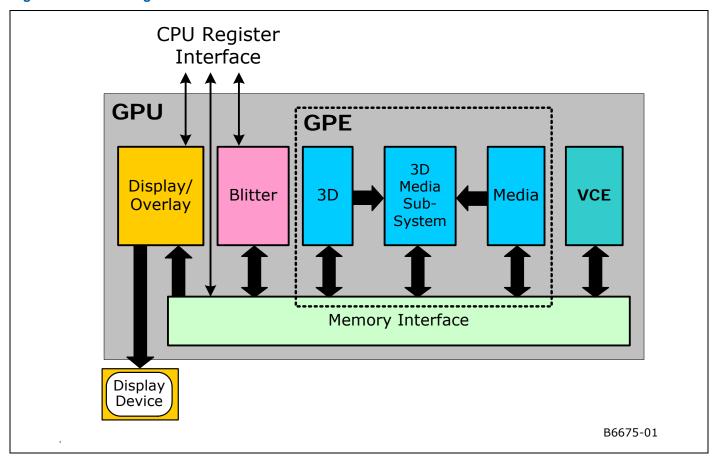

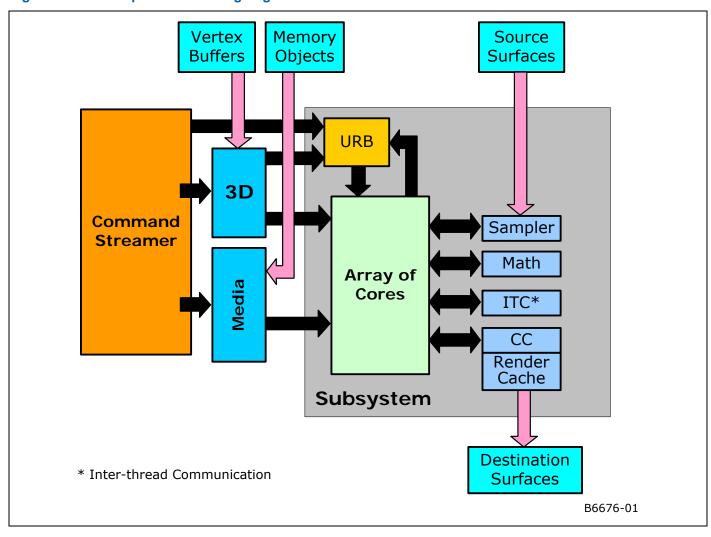

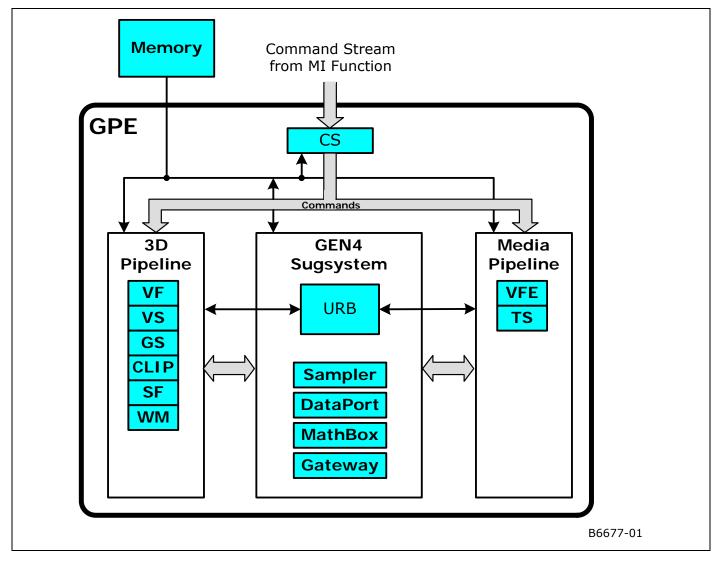

Volume 1, Part 1, 2, 3, 4 and 5 covers the overall Graphics Processing Unit (GPU), without much detail on 3D, Media, or the core subsystem. Topics include the command streamer, context switching, and memory access (including tiling). The Memory Data Formats can also be found in this volume.

The volume also contains a chapter on the Graphics Processing Engine (GPE). The GPE is a collective term for 3D, Media, the subsystem, and the parts of the memory interface that are used by these units. Display, blitter and their memory interfaces are *not* included in the GPE.

#### PRM, Volume 2: 3D/Media

Volume 2, Part 1, 2, 3 and 4 covers the 3D and Media pipelines in detail. This volume is where details for all of the "fixed functions" are covered, including commands processed by the pipelines, fixed-function state structures, and a definition of the inputs (payloads) and outputs of the threads spawned by these units.

This volume also covers the single Media Fixed Function, VLD. It describes how to initiate generic threads using the thread spawner (TS). It is generic threads which will be used for doing the majority of media functions. Programmable kernels will handle the algorithms for media functions such IDCT, Motion Compensation, and even Motion Estimation (used for encoding MPEG streams).

#### PRM, Volume 3: Display Registers

Volume 3, Part 1, 2, 3, and 4 describes the control registers for the display. The overlay registers and VGA registers are also cover in this volume.

#### PRM, Volume 4: Subsystem and Cores/Shared Functions

Volume 4, Part 1 and 2 describes the GMCH programmable cores, or EUs, and the "shared functions", which are shared by more than one EU and perform functions such as I/O and complex math functions.

The shared functions consist of the sampler: extended math unit, data port (the interface to memory for 3D and media), Unified Return Buffer (URB), and the Message Gateway which is used by EU threads to signal each other. The EUs use messages to send data to and receive data from the subsystem; the messages are described along with the shared functions although the generic message send EU instruction is described with the rest of the instructions in the Instruction Set Architecture (ISA) chapters.

This latter part of this volume describes the GMCH core, or EU, and the associated instructions that are used to program it. The instruction descriptions make up what is referred to as an Instruction Set Architecture, or ISA. The ISA describes all of the instructions that the GMCH core can execute, along with the registers that are used to store local data.

### **Device Tags and Chipsets**

Device "Tags" are used in various parts of this document as aliases for the device names/steppings, as listed in the following table. Note that stepping info is sometimes appended to the device tag, e.g., [DevBW-C]. Information without any device tagging is applicable to all devices/steppings.

**Table 1-1. Supported Chipsets**

| Chipset Family Name                                                                                                                                                                                       | Device<br>Name                                       | Device Tag                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------|

| Intel <sup>®</sup> Q965 Chipset<br>Intel <sup>®</sup> Q963 Chipset<br>Intel <sup>®</sup> G965 Chipset                                                                                                     | 82Q965<br>GMCH<br>82Q963<br>GMCH<br>82G965<br>GMCH   | [DevBW]                               |

| Intel® G35 Chipset                                                                                                                                                                                        | 82G35<br>GMCH                                        | [DevBW-E]                             |

| Mobile Intel <sup>®</sup> GME965 Express Chipset<br>Mobile Intel <sup>®</sup> GM965 Express Chipset<br>Mobile Intel <sup>®</sup> PM965 Express Chipset<br>Mobile Intel <sup>®</sup> GL960 Express Chipset | GM965<br>GMCH<br>GME965<br>GMCH                      | [DevCL]                               |

| Mobile Intel® GL40/GM45/GS40/GS45<br>Express Chipset                                                                                                                                                      | GL40<br>GM45<br>GS40<br>GS45                         | [DevCTG],<br>[DevCTG-A]<br>[DevCTG-B] |

| Intel® G41 Express Chipset Intel® G43 Express Chipset Intel® G45 Express Chipset Intel® Q43 Express Chipset Intel® Q45 Express Chipset                                                                    | G41<br>G43<br>G45<br>Q43<br>Q45                      | [DevEL]                               |

| Intel® HD Graphics For the all new 2010 Intel Core™ Processor Family                                                                                                                                      | Intel® Core™ i3 processor, Intel® Core™ i5 processor | [DevHVN/ABD]<br>[DevILK]<br>[DevIL]   |

#### NOTES:

- Unless otherwise specified, the information in this document applies to all of the devices mentioned in Table 1-1. For Information that does not apply to all devices, the Device Tag is used.

- 2. Throughout the PRM, references to "All" in a project field refters to all devices in

- 3. Throughout the PRM, references to [DevBW] apply to both [DevBW] and [DevBW-E]. [DevBW-E] is referenced specifically for information that is [DevBW-E] only.

- 4. Stepping info is sometimes appended to the device tag (e.g., [DevBW-C]). Information without any device tagging is applicable to all devices/steppings.

- 5. A shorthand is used to identify all devices/steppings prior to the device/stepping that the item pertains. Notations and Conventions.

# 1.1 Reserved Bits and Software Compatibility

In many register, instruction and memory layout descriptions, certain bits are marked as "Reserved". When bits are marked as reserved, it is essential for compatibility with future devices that software treat these bits as having a future, though unknown, effect. The behavior of reserved bits should be regarded as not only undefined, but unpredictable. Software should follow these guidelines in dealing with reserved bits:

Do not depend on the states of any reserved bits when testing values of registers that contain such bits. Mask out the reserved bits before testing. Do not depend on the states of any reserved bits when storing to instruction or to a register.

When loading a register or formatting an instruction, always load the reserved bits with the values indicated in the documentation, if any, or reload them with the values previously read from the register.

## 1.2 Terminology

| Term                           | Abbr. | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3D Pipeline                    |       | One of the two pipelines supported in the GPE. The 3D pipeline is a set of fixed-function units arranged in a pipelined fashion, which process 3D-related commands by spawning EU threads. Typically this processing includes rendering primitives. See 3D Pipeline.                                                                                                                                                                                                                                                                                                                                  |

| Adjacency                      |       | One can consider a single line object as existing in a strip of connected lines. The neighboring line objects are called "adjacent objects", with the non-shared endpoints called the "adjacent vertices." The same concept can be applied to a single triangle object, considering it as existing in a mesh of connected triangles. Each triangle shares edges with three other adjacent triangles, each defined by an non-shared adjacent vertex. Knowledge of these adjacent objects/vertices is required by some object processing algorithms (e.g., silhouette edge detection). See 3D Pipeline. |

| Application IP                 | AIP   | Application Instruction Pointer. This is part of the control registers for exception handling for a thread. Upon an exception, hardware moves the current IP into this register and then jumps to SIP.                                                                                                                                                                                                                                                                                                                                                                                                |

| Architectural Register<br>File | ARF   | A collection of architecturally visible registers for a thread such as address registers, accumulator, flags, notification registers, IP, null, etc. ARF should not be mistaken as just the address registers.                                                                                                                                                                                                                                                                                                                                                                                        |

| Array of Cores                 |       | Refers to a group of Genx EUs, which are physically organized in two or more rows. The fact that the EUs are arranged in an array is (to a great extent) transparent to CPU software or EU kernels.                                                                                                                                                                                                                                                                                                                                                                                                   |

| Binding Table                  |       | Memory-resident list of pointers to surface state blocks (also in memory).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Binding Table Pointer          | ВТР   | Pointer to a binding table, specified as an offset from the Surface State Base Address register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Bypass Mode                    |       | Mode where a given fixed function unit is disabled and forwards data down the pipeline unchanged. Not supported by all FF units.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Byte                           | В     | A numerical data type of 8 bits, B represents a signed byte integer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CBOX                           | СВОХ  | Cache Box (Ring stop at LLC).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Term                      | Abbr.     | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Child Thread              |           | A branch-node or a leaf-node thread that is created by another thread. It is a kind of thread associated with the media fixed function pipeline. A child thread is originated from a thread (the parent) executing on an EU and forwarded to the Thread Dispatcher by the TS unit. A child thread may or may not have child threads depending on whether it is a branch-node or a leaf-node thread. All pre-allocated resources such as URB and scratch memory for a child thread are managed by its parent thread. |

| Clip Space                |           | A 4-dimensional coordinate system within which a clipping frustum is defined. Object positions are projected from Clip Space to NDC space via "perspecitive divide" by the W coordinate, and then viewport mapped into Screen Space                                                                                                                                                                                                                                                                                 |

| Clipper                   |           | 3D fixed function unit that removes invisible portions of the drawing sequence by discarding (culling) primitives or by "replacing" primitives with one or more primitives that replicate only the visible portion of the original primitive.                                                                                                                                                                                                                                                                       |

| Color Calculator          | СС        | Part of the Data Port shared function, the color calculator performs fixed-<br>function pixel operations (e.g., blending) prior to writing a result pixel into<br>the render cache.                                                                                                                                                                                                                                                                                                                                 |

| Command                   |           | Directive fetched from a ring buffer in memory by the Command Streamer and routed down a pipeline. Should not be confused with instructions which are fetched by the instruction cache subsystem and executed on an EU.                                                                                                                                                                                                                                                                                             |

| Command Streamer          | CS or CSI | Functional unit of the Graphics Processing Engine that fetches commands, parses them and routes them to the appropriate pipeline.                                                                                                                                                                                                                                                                                                                                                                                   |

| Constant URB Entry        | CURBE     | A UE that contains "constant" data for use by various stages of the pipeline.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Control Register          | CR        | The read-write registers are used for thread mode control and exception handling for a thread.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Degenerate Object         |           | Object that is invisible due to coincident vertices or because does not intersect any sample points (usually due to being tiny or a very thin sliver).                                                                                                                                                                                                                                                                                                                                                              |

| Destination               |           | Describes an output or write operand.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Destination Size          |           | The number of data elements in the destination of a Genx SIMD instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Destination Width         |           | The size of each of (possibly) many elements of the destination of a GenxxSIMD instruction.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Double Quad word (DQword) | DQ        | A fundamental data type, DQ represents 16 bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Double word (DWord)       | D or DW   | A fundamental data type, D or DW represents 4 bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Drawing Rectangle         |           | A screen-space rectangle within which 3D primitives are rendered. An objects screen-space positions are relative to the Drawing Rectangle origin. See <i>Strips and Fans</i> .                                                                                                                                                                                                                                                                                                                                      |

| End of Block              | ЕОВ       | A 1-bit flag in the non-zero DCT coefficient data structure indicating the end of an 8x8 block in a DCT coefficient data buffer.                                                                                                                                                                                                                                                                                                                                                                                    |

| End Of Thread             | EOT       | A message sideband signal on the Output message bus signifying that the message requester thread is terminated. A thread must have at least one SEND instruction with the EOT bit in the message descriptor field set in order to properly terminate.                                                                                                                                                                                                                                                               |

| Exception                 |           | Type of (normally rare) interruption to EU execution of a thread's instructions. An exception occurrence causes the EU thread to begin executing the System Routine which is designed to handle exceptions.                                                                                                                                                                                                                                                                                                         |

| Term                          | Abbr.     | Definition                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Execution Channel             |           |                                                                                                                                                                                                                                                                                                                                                   |

| Execution Size                | ExecSize  | Execution Size indicates the number of data elements processed by a Genx SIMD instruction. It is one of the Genx instruction fields and can be changed per instruction.                                                                                                                                                                           |

| Execution Unit                | EU        | Execution Unit. An EU is a multi-threaded processor within the Genx multi-processor system. Each EU is a fully-capable processor containing instruction fetch and decode, register files, source operand swizzle and SIMD ALU, etc. An EU is also referred to as a Genx Core.                                                                     |

| Execution Unit<br>Identifier  | EUID      | The 4-bit field within a thread state register (SR0) that identifies the row and column location of the EU a thread is located. A thread can be uniquely identified by the EUID and TID.                                                                                                                                                          |

| Execution Width               | ExecWidth | The width of each of several data elements that may be processed by a single Genx SIMD instruction.                                                                                                                                                                                                                                               |

| Extended Math Unit            | EM        | A Shared Function that performs more complex math operations on behalf of several EUs.                                                                                                                                                                                                                                                            |

| FF Unit                       |           | A Fixed-Function Unit is the hardware component of a 3D Pipeline Stage. A FF Unit typically has a unique FF ID associated with it.                                                                                                                                                                                                                |

| Fixed Function                | FF        | Function of the pipeline that is performed by dedicated (vs. programmable) hardware.                                                                                                                                                                                                                                                              |

| Fixed Function ID             | FFID      | Unique identifier for a fixed function unit.                                                                                                                                                                                                                                                                                                      |

| FLT_MAX                       | fmax      | The magnitude of the maximum representable single precision floating number according to IEEE-754 standard. FLT_MAX has an exponent of 0xFE and a mantissa of all one's.                                                                                                                                                                          |

| Gateway                       | GW        | See Message Gateway.                                                                                                                                                                                                                                                                                                                              |

| GENX Core                     |           | Alternative name for an EU in the GENX multi-processor system.                                                                                                                                                                                                                                                                                    |

| General Register File         | GRF       | Large read/write register file shared by all the EUs for operand sources and destinations. This is the most commonly used read-write register space organized as an array of 256-bit registers for a thread.                                                                                                                                      |

| General State Base<br>Address |           | The Graphics Address of a block of memory-resident "state data", which includes state blocks, scratch space, constant buffers and kernel programs. The contents of this memory block are referenced via offsets from the contents of the General State Base Address register. See <i>Graphics Processing Engine</i> .                             |

| Geometry Shader               | GS        | Fixed-function unit between the vertex shader and the clipper that (if enabled) dispatches "geometry shader" threads on its input primitives. Application-supplied geometry shaders normally expand each input primitive into several output primitives in order to perform 3D modeling algorithms such as fur/fins. See <i>Geometry Shader</i> . |

| Graphics Address              |           | The GPE virtual address of some memory-resident object. This virtual address gets mapped by a SNBT or PSNBT to a physical memory address. Note that many memory-resident objects are referenced not with Graphics Addresses, but instead with offsets from a "base address register".                                                             |

| Graphics Processing Engine    | GPE       | Collective name for the Subsystem, the 3D and Media pipelines, and the Command Streamer.                                                                                                                                                                                                                                                          |

| GSR                           | GSR       | SNB CPU                                                                                                                                                                                                                                                                                                                                           |

| SNB                           | SNB       | Graphics Technology                                                                                                                                                                                                                                                                                                                               |

| Term                                 | Abbr.      | Definition                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SNBI                                 | SNBI       | The unit that handles the interface from SNB block to "external-to-SNB" world.                                                                                                                                                                                                                                               |

| SNBPMU                               | SNBPMU     | PM control within the SNB slice.                                                                                                                                                                                                                                                                                             |

| Guardband                            | GB         | Region that may be clipped against to make sure objects do not exceed the limitations of the renderer's coordinate space.                                                                                                                                                                                                    |

| Horizontal Stride                    | HorzStride | The distance in element-sized units between adjacent elements of a Genx region-based GRF access.                                                                                                                                                                                                                             |

| Immediate floating point vector      | VF         | A numerical data type of 32 bits, an immediate floating point vector of type VF contains 4 floating point elements with 8-bit each. The 8-bit floating point element contains a sign field, a 3-bit exponent field and a 4-bit mantissa field. It may be used to specify the type of an immediate operand in an instruction. |

| Immediate integer vector             | V          | A numerical data type of 32 bits, an immediate integer vector of type V contains 8 signed integer elements with 4-bit each. The 4-bit integer element is in 2's compliment form. It may be used to specify the type of an immediate operand in an instruction.                                                               |

| Index Buffer                         | IB         | Buffer in memory containing vertex indices.                                                                                                                                                                                                                                                                                  |

| In-loop Deblocking<br>Filter         | ILDB       | The deblocking filter operation in the decoding loop. It is a stage after MC in the video decoding pipe                                                                                                                                                                                                                      |

| Instance                             |            | In the context of the VF unit, an instance is one of a sequence of sets of similar primitive data. Each set has identical vertex data but may have unique instance data that differentiates it from other sets in the sequence.                                                                                              |

| Instruction                          |            | Data in memory directing an EU operation. Instructions are fetched from memory, stored in a cache and executed on one or more Genx cores. Not to be confused with commands which are fetched and parsed by the command streamer and dispatched down the 3D or Media pipeline.                                                |

| Instruction Pointer                  | IP         | The address (really an offset) of the instruction currently being fetched by an EU. Each EU has its own IP.                                                                                                                                                                                                                  |

| Instruction Set<br>Architecture      | ISA        | The GENX ISA describes the instructions supported by a GENX EU.                                                                                                                                                                                                                                                              |

| Instruction State<br>Cache           | ISC        | On-chip memory that holds recently-used instructions and state variable values.                                                                                                                                                                                                                                              |

| Interface Descriptor                 |            | Media analog of a State Descriptor.                                                                                                                                                                                                                                                                                          |

| Intermediate Z                       | IZ         | Completion of the Z (depth) test at the front end of the Windower/Masker unit when certain conditions are met (no alpha, no pixel-shader computed Z values, etc.)                                                                                                                                                            |

| Inverse Discrete<br>Cosine Transform | IDCT       | The stage in the video decoding pipe between IQ and MC                                                                                                                                                                                                                                                                       |

| Inverse Quantization                 | IQ         | A stage in the video decoding pipe between IS and IDCT.                                                                                                                                                                                                                                                                      |

| Inverse Scan                         | IS         | A stage in the video decoding pipe between VLD and IQ. In this stage, a sequence of none-zero DCT coefficients are converted into a block (e.g. an 8x8 block) of coefficients. VFE unit has fixed functions to support IS for MPEG-2.                                                                                        |

| Jitter                               |            | Just-in-time compiler.                                                                                                                                                                                                                                                                                                       |

| Term                             | Abbr. | Definition                                                                                                                                                                                                                    |

|----------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Kernel                           |       | A sequence of Genx instructions that is logically part of the driver or generated by the jitter. Differentiated from a Shader which is an application supplied program that is translated by the jitter to Genx instructions. |

| Least Significant Bit            | LSB   |                                                                                                                                                                                                                               |

| LLC                              | LLC   | Last Level Cache                                                                                                                                                                                                              |

| MathBox                          |       | See Extended Math Unit                                                                                                                                                                                                        |

| Media                            |       | Term for operations such as video decode and encode that are normally performed by the Media pipeline.                                                                                                                        |

| Media Pipeline                   |       | Fixed function stages dedicated to media and "generic" processing, sometimes referred to as the generic pipeline.                                                                                                             |

| Message                          |       | Messages are data packages transmitted from a thread to another thread, another shared function or another fixed function. Message passing is the primary communication mechanism of GENX architecture.                       |

| Message Gateway                  |       | Shared function that enables thread-to-thread message communication/synchronization used solely by the Media pipeline.                                                                                                        |

| Message Register<br>File         | MRF   | Write-only registers used by EUs to assemble messages prior to sending and as the operand of a send instruction.                                                                                                              |

| MLC                              | MLC   | Mid Level Cache                                                                                                                                                                                                               |

| Most Significant Bit             | MSB   |                                                                                                                                                                                                                               |

| Motion Compensation              | MC    | Part of the video decoding pipe.                                                                                                                                                                                              |

| Motion Picture Expert<br>Group   | MPEG  | MPEG is the international standard body JTC1/SC29/WG11 under ISO/IEC that has defined audio and video compression standards such as MPEG-1, MPEG-2, and MPEG-4, etc.                                                          |

| Motion Vector Field<br>Selection | MVFS  | A four-bit field selecting reference fields for the motion vectors of the current macroblock.                                                                                                                                 |

| Multi Render Targets             | MRT   | Multiple independent surfaces that may be the target of a sequence of 3D or Media commands that use the same surface state.                                                                                                   |

| Normalized Device<br>Coordinates | NDC   | Clip Space Coordinates that have been divided by the Clip Space "W" component.                                                                                                                                                |

| Object                           |       | A single triangle, line or point.                                                                                                                                                                                             |

| Open GL                          | OGL   | A Graphics API specification associated with Linux.                                                                                                                                                                           |

| Parent Thread                    |       | A thread corresponding to a root-node or a branch-node in thread generation hierarchy. A parent thread may be a root thread or a child thread depending on its position in the thread generation hierarchy.                   |

| PCU                              | PCU   | Power Control Unit                                                                                                                                                                                                            |

| Pipeline Stage                   |       | A abstracted element of the 3D pipeline, providing functions performed by a combination of the corresponding hardware FF unit and the threads spawned by that FF unit.                                                        |

| Pipelined State<br>Pointers      | PSP   | Pointers to state blocks in memory that are passed down the pipeline.                                                                                                                                                         |

| Pixel Shader                     | PS    | Shader that is supplied by the application, translated by the jitter and is dispatched to the EU by the Windower (conceptually) once per pixel.                                                                               |

|                                  | i     |                                                                                                                                                                                                                               |

| Term                                | Abbr. | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Point                               |       | A drawing object characterized only by position coordinates and width.                                                                                                                                                                                                                                                                                                                                                                              |

| Primitive                           |       | Synonym for object: triangle, rectangle, line or point.                                                                                                                                                                                                                                                                                                                                                                                             |

| Primitive Topology                  |       | A composite primitive such as a triangle strip, or line list. Also includes the objects triangle, line and point as degenerate cases.                                                                                                                                                                                                                                                                                                               |

| Provoking Vertex                    |       | The vertex of a primitive topology from which vertex attributes that are constant across the primitive are taken.                                                                                                                                                                                                                                                                                                                                   |

| Quad Quad word<br>(QQword)          | QQ    | A fundamental data type, QQ represents 32 bytes.                                                                                                                                                                                                                                                                                                                                                                                                    |

| Quad Word (QWord)                   | QW    | A fundamental data type, QW represents 8 bytes.                                                                                                                                                                                                                                                                                                                                                                                                     |

| Rasterization                       |       | Conversion of an object represented by vertices into the set of pixels that make up the object.                                                                                                                                                                                                                                                                                                                                                     |

| Region-based addressing             |       | Collective term for the register addressing modes available in the EU instruction set that permit discontiguous register data to be fetched and used as a single operand.                                                                                                                                                                                                                                                                           |

| Render Cache                        | RC    | Cache in which pixel color and depth information is written prior to being written to memory, and where prior pixel destination attributes are read in preparation for blending and Z test.                                                                                                                                                                                                                                                         |

| Render Target                       | RT    | A destination surface in memory where render results are written.                                                                                                                                                                                                                                                                                                                                                                                   |

| Render Target Array<br>Index        |       | Selector of which of several render targets the current operation is targeting                                                                                                                                                                                                                                                                                                                                                                      |

| Root Thread                         |       | A root-node thread. A thread corresponds to a root-node in a thread generation hierarchy. It is a kind of thread associated with the media fixed function pipeline. A root thread is originated from the VFE unit and forwarded to the Thread Dispatcher by the TS unit. A root thread may or may not have child threads. A root thread may have scratch memory managed by TS. A root thread with children has its URB resource managed by the VFE. |

| Sampler                             |       | Shared function that samples textures and reads data from buffers on behal of EU programs.                                                                                                                                                                                                                                                                                                                                                          |

| Scratch Space                       |       | Memory allocated to the subsystem that is used by EU threads for data storage that exceeds their register allocation, persistent storage, storage of mask stack entries beyond the first 16, etc.                                                                                                                                                                                                                                                   |

| Shader                              |       | A Genx program that is supplied by the application in a high level shader language, and translated to Genx instructions by the jitter.                                                                                                                                                                                                                                                                                                              |

| Shared Function                     | SF    | Function unit that is shared by EUs. EUs send messages to shared functions; they consume the data and may return a result. The Sampler, Data Port and Extended Math unit are all shared functions.                                                                                                                                                                                                                                                  |

| Shared Function ID                  | SFID  | Unique identifier used by kernels and shaders to target shared functions and to identify their returned messages.                                                                                                                                                                                                                                                                                                                                   |

| Single Instruction<br>Multiple Data | SIMD  | The term SIMD can be used to describe the kind of parallel processing architecture that exploits data parallelism at instruction level. It can also be used to describe the instructions in such architecture.                                                                                                                                                                                                                                      |

| Source                              |       | Describes an input or read operand                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Spawn                               |       | To initiate a thread for execution on an EU. Done by the thread spawner as well as most FF units in the 3D pipeline.                                                                                                                                                                                                                                                                                                                                |

| Term                          | Abbr. | Definition                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sprite Point                  |       | Point object using full range texture coordinates. Points that are not sprite points use the texture coordinates of the point's center across the entire point object.                                                                                                                                                                                                                                                             |

| State Descriptor              |       | Blocks in memory that describe the state associated with a particular FF, including its associated kernel pointer, kernel resource allowances, and a pointer to its surface state.                                                                                                                                                                                                                                                 |

| State Register                | SR    | The read-only registers containing the state information of the current thread, including the EUID/TID, Dispatcher Mask, and System IP.                                                                                                                                                                                                                                                                                            |

| State Variable                | SV    | An individual state element that can be varied to change the way given primitives are rendered or media objects processed. On Genx state variables persist only in memory and are cached as needed by rendering/processing operations except for a small amount of non-pipelined state.                                                                                                                                            |

| Stream Output                 |       | A term for writing the output of a FF unit directly to a memory buffer instead of, or in addition to, the output passing to the next FF unit in the pipeline. Currently only supported for the Geometry Shader (GS) FF unit.                                                                                                                                                                                                       |

| Strips and Fans               | SF    | Fixed function unit whose main function is to decompose primitive topologies such as strips and fans into primitives or objects.                                                                                                                                                                                                                                                                                                   |

| Sub-Register                  |       | Subfield of a SIMD register. A SIMD register is an aligned fixed size register for a register file or a register type. For example, a GRF register, 12, is 256-bit wide, 256-bit aligned register. A sub-register, 12.3:d, is the fourth dword of GRF register 12.                                                                                                                                                                 |

| Subsystem                     |       | The Genx name given to the resources shared by the FF units, including shared functions and EUs.                                                                                                                                                                                                                                                                                                                                   |

| Surface                       |       | A rendering operand or destination, including textures, buffers, and render targets.                                                                                                                                                                                                                                                                                                                                               |

| Surface State                 |       | State associated with a render surface including                                                                                                                                                                                                                                                                                                                                                                                   |