# Intel<sup>®</sup> HD Graphics OpenSource PRM

Volume 3 Part 4: PCH Display Registers [DevIBX]

For the all new 2010 Intel Core Processor Family Programmer's Reference Manual (PRM)

February 2009

Revision 1.0

IHD-OS-022810-R1V3PT4

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Sandy Bridge chipset family, Havendale/Auburndale chipset family, Intel<sup>®</sup> 965 Express Chipset Family, Intel<sup>®</sup> G35 Express Chipset, and Intel<sup>®</sup> 965GMx Chipset Mobile Family Graphics Controller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Intel and the Intel are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2010, Intel Corporation. All rights reserved.

# **Contents**

| 1. PCH Display Registers [DevIBX]                                                                                                      |           |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1.1 Introduction and Register Summary                                                                                                  |           |

| 1.1.1 Display Diagram                                                                                                                  |           |

| 1.1.2 Terminology                                                                                                                      |           |

| 1.1.3 Display Mode Set Sequence                                                                                                        |           |

| 1.1.4 Simultaneous Display Capabilities on a Single Display Pipe/Transcoder                                                            |           |

| 2. South Shared Functions (C0000h–CFFFFh)                                                                                              | 10        |

| 2.1 Interrupt Control Registers                                                                                                        |           |

| 2.1.1 South Display Engine Interrupt Registers Bit Definition<br>2.2 GMBUS and I/O Control Registers (C5000h–C5FFFh)                   | 10        |

| 2.2 GMBUS and I/O Control Registers (C5000h–C5FFFh)<br>2.2.1 GPIO Pin Usage (By Functions)                                             |           |

| 2.2.1 GPIO Pin Usage (By Punctions)                                                                                                    |           |

| 2.2.3 GMBUS Controller Programming Interface                                                                                           |           |

| 2.3 Display Clock Control Registers (C6000h–C6FFFH)                                                                                    |           |

| 2.4 Panel Power Sequencing Registers                                                                                                   |           |

| 2.5 Backlight Control Registers                                                                                                        |           |

|                                                                                                                                        |           |

| <ol> <li>South Transcoder and Port Controls (E0000h–EFFFFh)</li> <li>3.1 Transcoder A Timing</li> </ol>                                | <b>02</b> |

| 3.2 Transcoder A M/N Values                                                                                                            |           |

| 3.3 Transcoder A Video DIP                                                                                                             |           |

| 3.4 Transcoder B Timing                                                                                                                |           |

| 3.5 Transcoder B M/N Values                                                                                                            |           |

| 3.6 Transcoder B Video DIP                                                                                                             |           |

| 3.7 CRT DAC                                                                                                                            |           |

| 3.8 HDMI port C                                                                                                                        |           |

| 3.9 HDMI port D                                                                                                                        | 100       |

| 3.9.1 HDMID—Digital Display Port D Register                                                                                            | 100       |

| 3.10 LVDS                                                                                                                              | 104       |

| 4. South FDI Rx and Transcoder Control (F0000h–FBFFFh)                                                                                 | 110       |

| 4.1.1 Display Transcoder A Control                                                                                                     |           |

| 4.1.2 Display Transcoder B Control                                                                                                     | 112       |

| 4.1.3 FDI A Receiver Control                                                                                                           |           |

| 4.1.4 FDI B Receiver Control                                                                                                           | 120       |

| 4.2 HD Audio Registers (E2000h–E2FFFh)                                                                                                 |           |

| 4.2.1 Audio Configuration                                                                                                              |           |

| 4.2.2 AUD_CONFIG_A—Audio Configuration – Transcoder A                                                                                  |           |

| 4.2.3 AUD_CONFIG_B—Audio Configuration – Transcoder B                                                                                  |           |

| 4.2.4 AUD_MISC_CTRL_A—Audio MISC Control for Transcoder A                                                                              |           |

| 4.2.5 AUD_MISC_CTRL_B—Audio MISC Control for Transcoder B                                                                              |           |

| 4.2.6 AUD_VID_DID—Audio Vendor ID / Device ID                                                                                          |           |

| <ul> <li>4.2.7 AUD_RID—Audio Revision ID</li> <li>4.2.8 AUD_PWRST—Audio Power State (Function Group, Convertor, Pin Widget)</li> </ul> | 134       |

| 4.2.9 AUD_PORT_EN_HD_CFG — Audio Port Enable HDAudio Config                                                                            |           |

| 4.2.9 AOD_FORT_EN_ID_CFG — Audio Fort Enable TDAddio Coning                                                                            |           |

| 4.2.10 AOD_OUT_DIG_CNVT_A—Addio Digital Converter – Conv A                                                                             |           |

| 4.2.12 AUD_OUT_CH_STR—Audio Channel ID and Stream ID                                                                                   |           |

| 4.2.13 AUD_OUT_STR_DESC_A—Audio Stream Descriptor Format – Conv A                                                                      |           |

| 4.2.14 AUD_OUT_STR_DESC_B—Audio Stream Descriptor Format – Conv B        | 148 |

|--------------------------------------------------------------------------|-----|

| 4.2.15 AUD_PINW_CONNLNG_SEL—Audio Connection Select                      | 151 |

| 4.2.16 AUD_CNTL_ST_A—Audio Control State Register – Transcoder A         | 152 |

| 4.2.17 AUD_CNTL_ST_B—Audio Control State Register – Transcoder B         | 155 |

| 4.2.18 AUD_CNTL_ST2— Audio Control State 2                               | 157 |

| 4.2.19 AUD_HDMIW_STATUS—Audio HDMI Status                                | 159 |

| 4.2.20 AUD_HDMIW_HDMIEDID_A—HDMI Data EDID Block – Transcoder A          | 160 |

| 4.2.21 AUD_HDMIW_HDMIEDID_B—HDMI Data EDID Block – Transcoder B          | 161 |

| 4.2.22 AUD_HDMIW_INFOFR_A—Audio Widget Data Island Packet – Transcoder A | 161 |

| 4.2.23 AUD_HDMIW_INFOFR_B—Audio Widget Data Island Packet – Transcoder B | 162 |

| 4.3 DPB Control and Aux Channel                                          |     |

| 4.3.1 DPB—DisplayPort B Control Register                                 | 162 |

| 4.3.2 DPB_AUX_CH_CTL—Display Port B AUX Channel Control                  |     |

| 4.3.3 DPB_AUX_CH_DATA—Display Port B AUX Data Registers                  | 171 |

| 4.4 DPC Control and Aux Channel                                          |     |

| 4.4.1 DPC—Display Port C Control Register                                | 172 |

| 4.4.2 DPC_AUX_CH_CTL—Display Port C AUX Channel Control                  | 177 |

| 4.4.3 DPC_AUX_CH_DATA—Display Port C AUX Data Registers                  | 179 |

| 4.5 DPD Control and Aux Channel                                          | 179 |

| 4.5.1 DPD—DisplayPort D Control Register                                 | 180 |

| 4.5.2 DPD_AUX_CH_CTL—Display Port D AUX Channel Control                  | 185 |

| 4.5.3 DPD_AUX_CH_DATA—Display Port D AUX Data Registers                  | 187 |

| 4.6 DP_BUFTRANS—DisplayPort Buffer Translation                           |     |

| 5. South AFE Registers (FC000h–FFFFFh)                                   | 191 |

# **Revision History**

| Document Number       | Rev-<br>Number | Description     | Revision Date |

|-----------------------|----------------|-----------------|---------------|

| IHD-OS-022810_R1V3PT4 | 1.0            | Initial release | February 2010 |

**§§**

# 1. PCH Display Registers [DevIBX]

# **1.1 Introduction and Register Summary**

This chapter contains the register descriptions for the display portion of a family of integrated graphics devices. These registers do vary by devices within the family of devices so special attention needs to be paid to which devices use which registers and register fields.

Different devices within the family may add, modify, or delete registers or register fields relative to another device in the same family based on the supported functions of that device. Additional information on the use and programming of these registers can be found in the display chapter.

The following table contains the sections break down where the register information is contained within this chapter:

| Address Range | Description                    |

|---------------|--------------------------------|

| C0000h-CFFFFh | Shared Functions               |

| D0000h-DFFFFh | Messages                       |

| E0000h-EFFFFh | Transcoder and Port Controls   |

| F0000h-FBFFFh | Transcoder and FDI Rx Controls |

| FC000h-FFFFFh | AFE Registers                  |

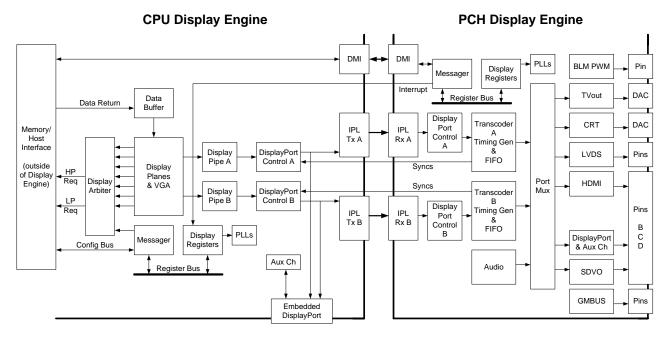

#### 1.1.1 Display Diagram

The display engine plane and pipe functions are in the CPU and most of the port functions are in the PCH.

FDI transfers pixel data from the CPU Display Engine (Tx - transmit side) to the PCH Display Engine (Rx - receive side). Sync signals control the pixel flow over FDI.

A pipe in the CPU Display Engine connects to a transcoder in the PCH Display Engine through the FDI interface.

The CPU Display Engine is also called the "North Display".

The PCH Display Engine is also called the "South Display".

## 1.1.2 Terminology

| Description                                      | Software Use                                                                                                                                                                                                                                                                                                                                                              | Should be implemented as                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read/Write                                       | This bit can be read or written.                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                     |

| Reserved:                                        | Don't assume a value for these bits. Writes have no effect.                                                                                                                                                                                                                                                                                                               | Writes are ignored. Reads return zero.                                                                                                                                                                                                                                                                              |

| Reserved: write as zero,<br>must be zero, or MBZ | Software must always write a zero to these<br>bits. This allows new features to be added<br>using these bits that will be disabled when<br>using old software and as the default case.                                                                                                                                                                                    | Writes are ignored. Reads return<br>zero. Maybe be connected as<br>Read/Write in future projects.                                                                                                                                                                                                                   |

| Reserved: software must preserve contents        | Software must write the original value back<br>to this bit. This allows new features to be<br>added using these bits.                                                                                                                                                                                                                                                     | Read only<br>Read/Write.                                                                                                                                                                                                                                                                                            |

| Read Only                                        | This bit is read only. The read value is determined by hardware. Writes to this bit have no effect.                                                                                                                                                                                                                                                                       | According to each specific bit. The<br>bit value is determined by hardware<br>and not affected by register writes<br>to the actual bit.                                                                                                                                                                             |

| Read/Clear                                       | This bit can be read and writes to it with a one cause the bit to clear.                                                                                                                                                                                                                                                                                                  | Hardware events cause the bit to<br>be set and the bit will be cleared on<br>a write operation where the<br>corresponding bit has a one for a<br>value.                                                                                                                                                             |

| Double Buffered                                  | Write when desired. Read gives the<br>unbuffered value (written value) unless<br>specified otherwise. Written values will<br>update to take effect after a certain point.<br>Some have a specific arming sequence<br>where a write to another register is required<br>before the update can take place. This is<br>used to ensure atomic updates of several<br>registers. | Two stages of registers used. First<br>stage is written into and used for<br>readback (unless specified<br>otherwise). First stage value is<br>transferred into second stage at the<br>update point. Second stage value<br>is used to control hardware.<br>Arm/disarm flag needed for specific<br>arming sequences. |

### 1.1.3 Display Mode Set Sequence

See the CPU Display Registers Bspec.

#### 1.1.4 Simultaneous Display Capabilities on a Single Display Pipe/Transcoder

|                      | Embedded<br>DP (on<br>CPU) | Inte-<br>grated<br>LVDS | DP          | Inte-<br>grated<br>TV | CRT       |

|----------------------|----------------------------|-------------------------|-------------|-----------------------|-----------|

| Embedded<br>DP (CPU) |                            | No (6)                  | No (6)      | No (6)                | No (6)    |

| Integrated<br>LVDS   |                            |                         | No (2, 7)   | No (1, 7)             | No (3, 7) |

| DP                   |                            |                         | No(3, 5, 7) | No (1, 7)             | No (4, 7) |

| Integrated<br>TV     |                            |                         |             |                       | No (1, 7) |

| CRT                  |                            |                         |             |                       |           |

Shading: Rose = Does not work, Yellow = Some cases work, Green = works

) TV Timings don't match.

2) No internal LVDS, HDMI or TV. DP optionally has SSC.

4) Only works if DP/HDMI is in 24bpp mode.

6) Digital ports are multiplexed on the same pins, only works if ports are different.

7) Embedded DP is on the CPU; can not share the link.

8) Dithering, range correction, and gamma are done in the CPU; the display with lower bpp can truncate or the display with higher bpp can lose bits. One of the displays dictates range and gamma.

9) No DisplayPort allowed with other port on the same pipe/transcoder.

10) No HDMI allowed with another HDMI on the same transcoder.

# 2. South Shared Functions (C0000h– CFFFFh)

# 2.1 Interrupt Control Registers

#### 2.1.1 South Display Engine Interrupt Registers Bit Definition

|                                         | South Display Engine Interrupt Control R                                                                                     | egisters Bit                               | Defir             | nition                                 |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------|----------------------------------------|

| Project:                                | All                                                                                                                          |                                            |                   |                                        |

| South Disp<br>together to<br>Registers. | lay Engine (SDE) interrupt bits come from events within the so generate the South/PCH Display Interrupt Event which will app | outh display engine<br>pear in the Display | e. The<br>y Engir | SDEIIR is ORed<br>ne Interrupt Control |

| The South                               | Display Engine Interrupt Control Registers all share the same I                                                              | bit definitions from                       | n this ta         | able.                                  |

| Bit                                     | Description                                                                                                                  |                                            |                   |                                        |

| 31:25                                   | Reserved Project: All                                                                                                        | For                                        | mat:              |                                        |

| 24                                      | Gmbus(combined)                                                                                                              | Project:                                   | All               | Format:                                |

|                                         | No IMR                                                                                                                       |                                            |                   |                                        |

| 23                                      | Reserved                                                                                                                     | Project:                                   | All               | Format:                                |

| 22                                      | Reserved                                                                                                                     | Project:                                   | All               | Format:                                |

| 21                                      | Audio_Transcoder_B                                                                                                           | Project:                                   | All               | Format:                                |

|                                         | Pulse?                                                                                                                       |                                            |                   |                                        |

| 20                                      | Audio_Transcoder_A                                                                                                           | Project:                                   | All               | Format:                                |

|                                         | Pulse?                                                                                                                       |                                            |                   |                                        |

| 19                                      | Poison                                                                                                                       | Project:                                   | All               | Format:                                |

|                                         | This is an active high pulse on receiving the poison message                                                                 | Э.                                         |                   |                                        |

| 18                                      | Performance_counter                                                                                                          | Project:                                   | All               | Format:                                |

|                                         | This is an active high pulse when the performance counter return the Performance Counter Source register                     | eaches the thresh                          | old val           | ue programmed in                       |

| 17                                      | FDI_RXB(combined)                                                                                                            | Project:                                   | All               | Format:                                |

|                                         | This is an active high level while any of the FDI_RXB_ISR bi                                                                 | its are set                                |                   |                                        |

| 16                                      | FDI_RXA(combined)                                                                                                            | Project:                                   | All               | Format:                                |

|                                         | This is an active high level while any of the FDI_RXA_ISR bi                                                                 | its are set                                |                   |                                        |

| 15                                      | AUX_Channel_D                                                                                                                | Project:                                   | All               | Format:                                |

|                                         | This is an active high pulse on the AUX D done event                                                                         |                                            |                   |                                        |

|    | South Display Engine Interrupt Control Reg                        | jisters Bit     | Defir    | nition  |

|----|-------------------------------------------------------------------|-----------------|----------|---------|

| 14 | AUX_Channel_C                                                     | Project:        | All      | Format: |

|    | This is an active high pulse on the AUX C done event              |                 |          |         |

| 13 | AUX_Channel_B                                                     | Project:        | All      | Format: |

|    | This is an active high pulse on the AUX B done event              |                 |          |         |

| 12 | Reserved Project: All                                             | For             | mat:     |         |

| 11 | CRT_Hotplug                                                       | Project:        | All      | Format: |

|    | This is an active high level while either of the CRT Hot Plug Det | ection Status b | oits are | e set.  |

| 10 | Reserved                                                          | Project:        | All      | Format: |

| 9  | Reserved                                                          | Project:        | All      | Format: |

| 8  | Reserved                                                          | Project:        | All      | Format: |

| 7  | Reserved Project: All                                             | For             | mat:     |         |

| 6  | Reserved                                                          | Project:        | All      | Format: |

| 5  | Transcoder_B_CRC_done                                             | Project:        | All      | Format: |

|    | This is an active high pulse on the Transcoder B CRC done.        |                 |          |         |

| 4  | Transcoder_B_CRC_error                                            | Project:        | All      | Format: |

|    | This is an active high pulse on the Transcoder B CRC error.       |                 |          |         |

| 3  | Transcoder_B_FIFO_underrun                                        | Project:        | All      | Format: |

|    | This is an active high level for the duration of the Transcoder B | FIFO underrun   | n        |         |

| 2  | Transcoder_A_CRC_done                                             | Project:        | All      | Format: |

|    | This is an active high pulse on the Transcoder A CRC done.        |                 |          |         |

| 1  | Transcoder_A_CRC_error                                            | Project:        | All      | Format: |

|    | This is an active high pulse on the Transcoder A CRC error.       |                 |          |         |

| 0  | Transcoder_A_FIFO_underrun                                        | Project:        | All      | Format: |

|    | This is an active high level for the duration of the Transcoder A | FIFO underrun   | n        |         |

### 2.1.1.1 SDEISR — South Display Engine Interrupt Status Register

|                    | SD            | EISR — South Disp                                       | lay Engine Interrupt Status R                                                                                                | egister                    |  |  |  |

|--------------------|---------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|

| Register Ty        | ype: MN       | ЛЮ                                                      |                                                                                                                              |                            |  |  |  |

|                    |               | set: C4000h                                             |                                                                                                                              |                            |  |  |  |

| Project:           | All           |                                                         |                                                                                                                              |                            |  |  |  |

| <b>Default Val</b> | lue: 000      | 00000h                                                  |                                                                                                                              |                            |  |  |  |

| Access:            | Re            | ad Only                                                 |                                                                                                                              |                            |  |  |  |

| Size (in bit       | <b>s):</b> 32 |                                                         |                                                                                                                              |                            |  |  |  |

| of these int       | errupt co     | nditions are reported in th                             | value of all interrupt status bits. The II<br>te persistent IIR (i.e., set bits must be<br>IIR bits to cause CPU interrupts. |                            |  |  |  |

| Bit                |               |                                                         | Description                                                                                                                  |                            |  |  |  |

| 31:0               | South_D       | isplay_Engine_Interrupt_S                               | Status_Bits                                                                                                                  |                            |  |  |  |

|                    | Project:      | All                                                     |                                                                                                                              |                            |  |  |  |

|                    | Format:       | South Display Engine Ir                                 | nterrupt Control Registers Bit Definition                                                                                    | See description above      |  |  |  |

|                    | This field    | contains the non-persistent                             | values of all interrupt status bits.                                                                                         |                            |  |  |  |

|                    | Value         | Name                                                    | Description                                                                                                                  | Project                    |  |  |  |

|                    | 0b            | Condition Doesn't Exist                                 | Interrupt Condition currently does not e                                                                                     | exist All                  |  |  |  |

| 1                  | 1b            | Condition Exists                                        | Interrupt Condition currently exists                                                                                         | All                        |  |  |  |

|                    | Progra        | mming Notes                                             |                                                                                                                              |                            |  |  |  |

|                    |               | nputs to this register are sho<br>ble these conditions. | rt pulses; therefore software should not ex                                                                                  | xpect to use this register |  |  |  |

### 2.1.1.2 DEIMR — South Display Engine Interrupt Mask Register

|                    | S                   | DEIMR — So         | outh Display Engine Interrupt Mask Register                                                                                              |         |

|--------------------|---------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Register Ty        | <mark>ype:</mark> M | MIO                |                                                                                                                                          |         |

| Address O          | ffset: C4           | 4004h              |                                                                                                                                          |         |

| Project:           | AI                  | I                  |                                                                                                                                          |         |

| <b>Default Val</b> | ue: Ff              | FEDFFFh            |                                                                                                                                          |         |

| Access:            | R                   | /W                 |                                                                                                                                          |         |

| Size (in bit       | <mark>s):</mark> 32 | 2                  |                                                                                                                                          |         |

|                    | ntil clear          | ed by software.    | be reported in the IIR, possibly triggering a CPU interrupt, and w<br>"Masked" bits will not be reported in the IIR and therefore cannot |         |

| Bit                |                     |                    | Description                                                                                                                              |         |

| 31:0               | South_              | Display_Engine     | _Interrupt_Mask_Bits                                                                                                                     |         |

|                    | Project:            | All                |                                                                                                                                          |         |

|                    | Format:             | South Displ        | ay Engine Interrupt Control Registers Bit Definition See description a                                                                   | bove    |

|                    | This fiel           | d contains a bit m | nask which selects which interrupt bits from the ISR are reported in the I                                                               | IR.     |

|                    | Value               | Name               | Description                                                                                                                              | Project |

|                    | 0b                  | Not Masked         | Will be reported in the IIR                                                                                                              | All     |

|                    | 1b                  | Masked             | Will not be reported in the IIR                                                                                                          | All     |

### 2.1.1.3 SDEIIR — South Display Engine Interrupt Identity Register

|                             | SD                       | EIIR — South Displa            | ay Engine Interrupt Identity Register                                                                                                                                                   |              |  |  |

|-----------------------------|--------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|

| Register Type: MMIO         |                          |                                |                                                                                                                                                                                         |              |  |  |

| <b>.</b> .                  | ffset: C4008h            |                                |                                                                                                                                                                                         |              |  |  |

| Project:                    | All                      |                                |                                                                                                                                                                                         |              |  |  |

| Default Va                  | ue: 00                   | 00000h                         |                                                                                                                                                                                         |              |  |  |

| Access:                     | R/\                      | N Clear                        |                                                                                                                                                                                         |              |  |  |

| Size (in bit                | <b>s):</b> 32            |                                |                                                                                                                                                                                         |              |  |  |

| interrupts (<br>interrogate | if enablec<br>d to deter | I via the IER). When a CF      | are "unmasked" by the IMR and thus can generat<br>PU interrupt is generated, this should be the first re<br>errupt. Writing a '1' into the appropriate bit pos                          | gister to be |  |  |

| Bit                         |                          | <b>-</b>                       | Description                                                                                                                                                                             |              |  |  |

| 31:0                        | South_D                  | )<br>isplay_Engine_Interrupt_I | dentity_Bits                                                                                                                                                                            |              |  |  |

|                             | Project:                 | All                            |                                                                                                                                                                                         |              |  |  |

|                             | Format:                  | South Display Engine In        | terrupt Control Registers Bit Definition See description                                                                                                                                | on above     |  |  |

|                             | IMR. If e<br>register v  | nabled by the IER, bits set in | of the interrupt bits from the ISR which are "unmasked"<br>n this register will generate a CPU interrupt. Bits set in t<br>the interrupt condition is "cleared" via software by writing | his          |  |  |

|                             | Value                    | Name                           | Description                                                                                                                                                                             | Project      |  |  |

|                             | 0b                       | Condition Not Detected         | Interrupt Condition Not Detected                                                                                                                                                        | All          |  |  |

|                             | 1b                       | Condition Detected             | Interrupt Condition Detected (may or may not have<br>actually generated a CPU interrupt)                                                                                                | All          |  |  |

### 2.1.1.4 SDEIER — South Display Engine Interrupt Enable Register

|                    | SD             | EIER —      | South Display Engine Interrupt Enable Register                                                                               |                  |

|--------------------|----------------|-------------|------------------------------------------------------------------------------------------------------------------------------|------------------|

| Register Ty        | <b>/pe:</b> MI | NIO         |                                                                                                                              |                  |

| Address O          | ffset: C4      | 00Ch        |                                                                                                                              |                  |

| Project:           | All            |             |                                                                                                                              |                  |

| <b>Default Val</b> | <b>ue:</b> 00  | 000000h     |                                                                                                                              |                  |

| Access:            | R/             | W           |                                                                                                                              |                  |

| Size (in bit       | <b>s):</b> 32  |             |                                                                                                                              |                  |

|                    | •              |             | terrupt enable bit for each interrupt bit in the IIR register. A di Identity Register to allow polling of interrupt sources. | sabled interrupt |

| Bit                |                |             | Description                                                                                                                  |                  |

| 31:0               | South_[        | Display_Eng | gine_Interrupt_Enable_Bits                                                                                                   |                  |

|                    | Project:       | All         |                                                                                                                              |                  |

|                    | Format:        | South I     | Display Engine Interrupt Control Registers Bit Definition See descr                                                          | iption above     |

|                    |                |             | ter enable a CPU interrupt to be generated whenever the correspond gister becomes set.                                       | ing bit in the   |

|                    | Value          | Name        | Description                                                                                                                  | Project          |

|                    | 0b             | Disable     | Disable                                                                                                                      | All              |

|                    | 1b             | Enable      | Enable                                                                                                                       | All              |

## 2.1.1.5 Digital Port Hot Plug Control Register

|                                                                             |                                                                                                                                   |                             | Digital Port Hot Plug Control Register                                    |            |  |  |  |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------|------------|--|--|--|

| Register T<br>Address C<br>Project:<br>Default Va<br>Access:<br>Size (in bi | Offset: C4<br>All<br>Ilue: 000<br>R/\                                                                                             | /IO<br>030h<br>000000h<br>N |                                                                           |            |  |  |  |

| Bit                                                                         |                                                                                                                                   |                             | Description                                                               |            |  |  |  |

| 31:21                                                                       | Reserve                                                                                                                           | <b>d</b> Proj               | ject: All Format:                                                         |            |  |  |  |

| 20                                                                          | Digital_F                                                                                                                         | ort_D_Ho                    | t_Plug_Detect_Input_Enable                                                |            |  |  |  |

|                                                                             | Project:                                                                                                                          |                             | All                                                                       |            |  |  |  |

|                                                                             | Default V                                                                                                                         | /alue:                      | 0b                                                                        |            |  |  |  |

|                                                                             | Controls the state of the HPD buffer for the digital port. The buffer state is independent of whether the port is enabled or not. |                             |                                                                           |            |  |  |  |

|                                                                             | Value                                                                                                                             | Name                        | Description                                                               | Project    |  |  |  |

|                                                                             | 0b                                                                                                                                | Disable                     | Buffer disabled                                                           | All        |  |  |  |

|                                                                             | 1b                                                                                                                                | Enable                      | Buffer enabled. Hot plugs bit reflect the electrical state of the HPD pin | All        |  |  |  |

| 19:18                                                                       | Digital_Port_D_Hot_Plug_Short_Pulse_Duration                                                                                      |                             |                                                                           |            |  |  |  |

|                                                                             | Project:                                                                                                                          |                             | All                                                                       |            |  |  |  |

|                                                                             | Default V                                                                                                                         | /alue:                      | 0b                                                                        |            |  |  |  |

|                                                                             | These bit                                                                                                                         | ts define the               | e duration of the pulse defined as a short pulse.                         |            |  |  |  |

|                                                                             | Malara                                                                                                                            | Name                        | Description                                                               | Project    |  |  |  |

|                                                                             | Value                                                                                                                             |                             |                                                                           |            |  |  |  |

|                                                                             | 00b                                                                                                                               | 2ms                         | 2mS                                                                       | All        |  |  |  |

|                                                                             |                                                                                                                                   |                             | 2mS<br>4.5mS                                                              | All<br>All |  |  |  |

|                                                                             | 00b                                                                                                                               | 2ms                         | -                                                                         |            |  |  |  |

|       |                          | I                            | Digital Po       | rt Hot Plug Control Register                                                                                                                                                                                    |          |

|-------|--------------------------|------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 17:16 | Digital_P                | ort_D_Hot                    | _Plug_Interr     | upt_Detect_Status                                                                                                                                                                                               |          |

|       | Project:                 |                              | All              |                                                                                                                                                                                                                 |          |

|       | Default Va               | alue:                        | 0b               |                                                                                                                                                                                                                 |          |

|       | to clear th<br>When eith | ne status. T<br>ner a long c | This bit is used | o on the digital port. Graphics software must write a one to t<br>d for either monitor hotplug/unplug or for notification of a sin<br>is detected, one of these bits will set. These bits are ORed<br>ster bit. | k event. |

|       | Value                    | Name                         |                  | Description                                                                                                                                                                                                     | Project  |

|       | 00b                      | No Detec                     | t                | Digital port hot plug event not detected                                                                                                                                                                        | All      |

|       | X1b                      | Short Det                    | ect              | Digital port short pulse hot plug event detected                                                                                                                                                                | All      |

|       | 1Xb                      | Long Det                     | ect              | Digital port long pulse hot plug event detected                                                                                                                                                                 | All      |

| 15:13 | Reserved                 | <b>l</b> Proje               | ect: All         | Format:                                                                                                                                                                                                         |          |

| 12    | Digital_P                | ort_C_Hot                    | _Plug_Detec      | t_Input_Enable                                                                                                                                                                                                  |          |

|       | Project:                 |                              | All              |                                                                                                                                                                                                                 |          |

|       | Default Va               | alue:                        | 0b               |                                                                                                                                                                                                                 |          |

|       |                          | he state of abled or no      |                  | er for the digital port. The buffer state is independent of whe                                                                                                                                                 | ther the |

|       | Value                    | Name                         | Description      | 1                                                                                                                                                                                                               | Project  |

|       | 0b                       | Disable                      | Buffer disat     | bled                                                                                                                                                                                                            | All      |

|       | 1b                       | Enable                       | Buffer enab      | led. Hot plugs bit reflect the electrical state of the HPD pin                                                                                                                                                  | All      |

| 11:10 | Digital_P                | ort_C_Hot                    | _Plug_Short      | _Pulse_Duration                                                                                                                                                                                                 |          |

|       | Project:                 |                              | All              |                                                                                                                                                                                                                 |          |

|       | Default Va               | alue:                        | 0b               |                                                                                                                                                                                                                 |          |

|       | These bits               | s define the                 | e duration of th | ne pulse defined as a short pulse.                                                                                                                                                                              |          |

|       | Value                    | Name                         | Description      | ı                                                                                                                                                                                                               | Project  |

|       | 00b                      | 2ms                          | 2mS              |                                                                                                                                                                                                                 | All      |

|       | 01b                      | 4.5ms                        | 4.5mS            |                                                                                                                                                                                                                 | All      |

|       | 10b                      | 6ms                          | 6mS              |                                                                                                                                                                                                                 | All      |

|       | 11b                      | 100ms                        | 100mS            |                                                                                                                                                                                                                 | All      |

|       |                          |                              |                  |                                                                                                                                                                                                                 |          |

| 9:8 | Digital F                                                                                                                                                                                                                                                                                                                                                                   | ort C Hot Plu                                                         | Ig_Interrupt_Detect_Status                                                                            |                            |  |  |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|--|--|

|     | Project:                                                                                                                                                                                                                                                                                                                                                                    |                                                                       | All                                                                                                   |                            |  |  |  |  |  |

|     | Default Value: 0b                                                                                                                                                                                                                                                                                                                                                           |                                                                       |                                                                                                       |                            |  |  |  |  |  |

|     | This reflects hot plug detect status on the digital port. Graphics software must write a one to these bits to clear the status. This bit is used for either monitor hotplug/unplug or for notification of a sink event. When either a long or short pulse is detected, one of these bits will set. These bits are ORed together to go to the main ISR hotplug register bit. |                                                                       |                                                                                                       |                            |  |  |  |  |  |

|     | Value                                                                                                                                                                                                                                                                                                                                                                       | Name                                                                  | Description                                                                                           | Project                    |  |  |  |  |  |

|     | 00b                                                                                                                                                                                                                                                                                                                                                                         | No Detect                                                             | Digital port hot plug event not detected                                                              | All                        |  |  |  |  |  |

|     | X1b                                                                                                                                                                                                                                                                                                                                                                         | Short Detect                                                          | Digital port short pulse hot plug event detected                                                      | All                        |  |  |  |  |  |

|     | 1Xb                                                                                                                                                                                                                                                                                                                                                                         | Long Detect                                                           | Digital port long pulse hot plug event detected                                                       | All                        |  |  |  |  |  |

| 7:5 | Reserve                                                                                                                                                                                                                                                                                                                                                                     | d Project:                                                            | All Format:                                                                                           |                            |  |  |  |  |  |

| 4   | -                                                                                                                                                                                                                                                                                                                                                                           | ort_B_Hot_Plu                                                         | Ig_Detect_Input_Enable                                                                                |                            |  |  |  |  |  |

|     | Project:                                                                                                                                                                                                                                                                                                                                                                    |                                                                       | All                                                                                                   |                            |  |  |  |  |  |

|     | Default V                                                                                                                                                                                                                                                                                                                                                                   |                                                                       | 0b                                                                                                    |                            |  |  |  |  |  |

|     | Controls the state of the HPD buffer for the digital port. The buffer state is independent of whether the port is enabled or not.                                                                                                                                                                                                                                           |                                                                       |                                                                                                       |                            |  |  |  |  |  |

|     | Value                                                                                                                                                                                                                                                                                                                                                                       | Name De                                                               | escription                                                                                            | Project                    |  |  |  |  |  |

|     | 0b                                                                                                                                                                                                                                                                                                                                                                          | Disable Bu                                                            | iffer disabled                                                                                        | All                        |  |  |  |  |  |

|     | 1b                                                                                                                                                                                                                                                                                                                                                                          | Enable Bu                                                             | ffer enabled. Hot plugs bit reflect the electrical state of the HPD pin                               | All                        |  |  |  |  |  |

| 3:2 | Digital_Port_B_Hot_Plug_Short_Pulse_Duration                                                                                                                                                                                                                                                                                                                                |                                                                       |                                                                                                       |                            |  |  |  |  |  |

|     |                                                                                                                                                                                                                                                                                                                                                                             | These bits define the duration of the pulse defined as a short pulse. |                                                                                                       |                            |  |  |  |  |  |

|     |                                                                                                                                                                                                                                                                                                                                                                             | 00 = 2mS (Default)                                                    |                                                                                                       |                            |  |  |  |  |  |

|     | <b>01</b> = 4.5r                                                                                                                                                                                                                                                                                                                                                            | -                                                                     |                                                                                                       |                            |  |  |  |  |  |

|     | <b>10</b> = 6mS                                                                                                                                                                                                                                                                                                                                                             |                                                                       |                                                                                                       |                            |  |  |  |  |  |