# Intel<sup>®</sup> OpenSource HD Graphics Programmer's Reference Manual (PRM) Volume 1 Part 5: Graphics Core – Blitter Engine (SandyBridge)

# For the 2011 Intel Core Processor Family

May 2011 Revision 1.0

#### NOTICE:

This document contains information on products in the design phase of development, and Intel reserves the right to add or remove product features at any time, with or without changes to this open source documentation.

#### **Creative Commons License**

You are free to Share — to copy, distribute, display, and perform the work

#### Under the following conditions:

**Attribution**. You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

No Derivative Works. You may not alter, transform, or build upon this work.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The SandyBridge chipset family, Havendale/Auburndale chipset family, Intel<sup>®</sup> 965 Express Chipset Family, Intel<sup>®</sup> G35 Express Chipset, and Intel<sup>®</sup> 965GMx Chipset Mobile Family Graphics Controller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel<sup>®</sup> sales office or your distributor to obtain the latest specifications and before placing your product order. I2C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I2C bus/protocol and was developed by Intel<sup>®</sup>. Implementations of the I2C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

**Copyright © 2011, Intel Corporation. All rights reserved.**

# Contents

| 1. BLT Engine                                                    | 5  |

|------------------------------------------------------------------|----|

| 1.1 Introduction                                                 | 5  |

| 1.2 Classical BLT Engine Functional Description                  | 5  |

| 1.2.1 Basic BLT Functional Considerations                        |    |

| 1.2.2 Basic Graphics Data Considerations                         |    |

| 1.2.3 BLT Programming Examples                                   | 23 |

| 1.3 BLT Instruction Overview                                     | 29 |

| 1.4 BLT Engine State                                             | 29 |

| 1.5 Cacheable Memory Support                                     | 30 |

| 1.6 Device Cache Coherency: Render & Texture Caches              |    |

| 1.7 BLT Engine Instructions                                      |    |

| 1.7.1 Blt Programming Restrictions                               |    |

| 1.8 Fill/Move Instructions                                       |    |

| 1.8.1 COLOR_BLT (Fill)                                           |    |

| 1.8.2 SRC_COPY_BLT (Move)                                        | 32 |

| 1.9 2D (X,Y) BLT Instructions                                    |    |

| 1.9.1 XY_SETUP_BLT                                               |    |

| 1.9.2 XY_SETUP_MONO_PATTERN_SL_BLT                               |    |

| 1.9.3 XY_SETUP_CLIP_ BLT                                         |    |

| 1.9.4 XY_PIXEL_BLT                                               |    |

| 1.9.5 XY_SCANLINES_BLT                                           |    |

| 1.9.6 XY_TEXT_BLT                                                |    |

| 1.9.7 XY_TEXT_IMMEDIATE_BLT                                      | 40 |

| 1.9.8 XY_COLOR_BLT                                               | 41 |

| 1.9.9 XY_PAT_BLT                                                 |    |

| 1.9.10 XY_PAT_CHROMA_BLT                                         |    |

| 1.9.11 XY_PAT_BLT_IMMEDIATE                                      |    |

| 1.9.12 XY_PAT_CHROMA_BLT_IMMEDIATE                               | 46 |

| 1.9.13 XY_MONO_PAT_BLT                                           |    |

| 1.9.14 XY_MONO_PAT_FIXED_BLT                                     | 49 |

| 1.9.15 XY_SRC_COPY_BLT                                           |    |

| 1.9.16 XY_SRC_COPY_CHROMA_BLT                                    | 58 |

| 1.9.17 XY_MONO_SRC_COPY_BLT                                      | 60 |

| 1.9.18 XY_MONO_SRC_COPY_ IMMEDIATE_BLT                           | 61 |

| 1.9.19 XY_FULL_BLT                                               | 62 |

| 1.9.20 XY_FULL_IMMEDIATE_PATTERN_BLT                             |    |

| 1.9.21 XY_FULL_MONO_SRC_BLT                                      |    |

| 1.9.22 XY_FULL_MONO_SRC_IMMEDIATE_PATTERN_BLTBLT                 | 67 |

| 1.9.23 XY_FULL_MONO_PATTERN_BLT                                  | 69 |

| 1.9.24 XY_FULL_MONO_PATTERN_MONO_SRC_BLT                         |    |

| 1.10 BLT Engine Instruction Field Definitions                    | 73 |

| 1.10.1 BR00—BLT Opcode & Control                                 |    |

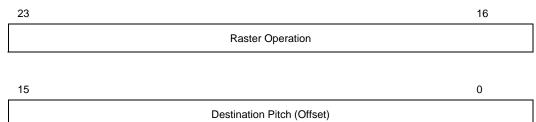

| 1.10.2 BR01—Setup BLT Raster OP, Control, and Destination Offset | 76 |

| 1.10.3 BR05—Setup Expansion Background Color                     |    |

| 1.10.4 BR06—Setup Expansion Foreground Color                     |    |

| 1.10.5 BR07—Setup Color Pattern Address                          |    |

| 1.10.6 BR09—Destination Address                                  |    |

| 1.10.7 BR11—BLT Source Pitch (Offset)                            |    |

| 1.10.8 BR12—Source Address                                       |    |

| 1.10.9 BR13—BLT Raster OP, Control, and Destination Pitch        | 82 |

| 1.10.10   | BR14—Destination Width and Height                           |  |

|-----------|-------------------------------------------------------------|--|

| 1.10.11   | BR15—Color Pattern Address                                  |  |

| 1.10.12   | 2 BR16—Pattern Expansion Background and Solid Pattern Color |  |

| 1.10.13   | BR17—Pattern Expansion Foreground Color                     |  |

| 1.10.14   | BR18—Source Expansion Background, and Destination Color     |  |

| 1.10.15   | BR19—Source Expansion Foreground Color                      |  |

| 2. Blitte | er (Blt) Engine Command Streamer                            |  |

| 2.1 Re    | gisters for Blitter Engine                                  |  |

| 2.1.1     | Introduction                                                |  |

| 2.1.2     | GAB PWR CTX STORAGE REGISTERS                               |  |

| 2.1.3     | Virtual Memory Control                                      |  |

| 2.1.4     | Mode and Misc Ctrl Registers                                |  |

| 2.1.5     | BCS_RINGBUF—Ring Buffer Registers                           |  |

| 2.1.6     | Interrupt Control Registers                                 |  |

| 2.1.7     | Logical Context Support                                     |  |

| 2.1.8     | Software Control Bit Definitions                            |  |

| 2.2 Me    | mory Interface Commands for Blitter Engine                  |  |

| 2.2.1     | Introduction                                                |  |

| 2.2.2     | MI_ARB_CHECK                                                |  |

| 2.2.3     | MI_BATCH_BUFFER_END                                         |  |

| 2.2.4     | MI_BATCH_BUFFER_START                                       |  |

| 2.2.5     | MI_FLUSH_DW                                                 |  |

| 2.2.6     | MI_LOAD_REGISTER_IMM                                        |  |

| 2.2.7     | MI_NOOP                                                     |  |

| 2.2.8     | MI_REPORT_HEAD                                              |  |

| 2.2.9     | MI_SEMAPHORE_MBOX                                           |  |

| 2.2.10    | MI_STORE_REGISTER_MEM                                       |  |

| 2.2.11    | MI_STORE_DATA_IMM                                           |  |

| 2.2.12    | MI_STORE_DATA_INDEX                                         |  |

| 2.2.13    | MI_SUSPEND_FLUSH                                            |  |

| 2.2.14    |                                                             |  |

| 2.2.15    | MI_USER_INTERRUPT                                           |  |

| 2.2.16    | MI_WAIT_FOR_EVENT [DevSNB]                                  |  |

| 2.2.17    | MSG_LOAD_SL – Load Scan Lines Message                       |  |

# 1. BLT Engine

# 1.1 Introduction

2D Rendering can be divided into 2 categories: classical BLTs, described here, and 3D BLTs.

3D BLTs are operations which can take advantage of the 3D drawing engine's functionality and access patterns. Functions such as Alpha BLTs, arithmetic (bilinear) stretch BLTs, rotations, transposing pixel maps, color space conversion, and DIBs are all considered 3D BLTs and are covered in the 3D rendering section. DIBs can be thought of as an indexed texture which uses the texture palette for performing the data translation. All drawing engines have swappable context. The same hardware can be used by multiple driver threads where the current state of the hardware is saved to memory and the appropriate state is loaded from memory on thread switches.

All operands for both 3D and classical BLTs can be in graphics aperture or cacheable system memory. Some operands can be immediates which are sent through the command stream. Immediate operands are: patterns, monochrome sources, DIB palettes, and DIB source operands. All non-monochrome operands which are not tiled have a stride granularity of a double-word (4 bytes).

The classical BLT commands support both linear addressing and X, Y coordinates with and without clipping. All X1 and Y1 destination and clipping coordinates are inclusive, while X2 and Y2 are exclusive. Currently, only destination coordinates can be negative. The source and clipping coordinates must be positive. If clipping is disabled, but a negative destination coordinate is specified, the negative coordinate is clipped to 0. Linear address BLT commands must supply a non-zero height and width. If either height or width = 0, then no accesses occur.

# **1.2 Classical BLT Engine Functional Description**

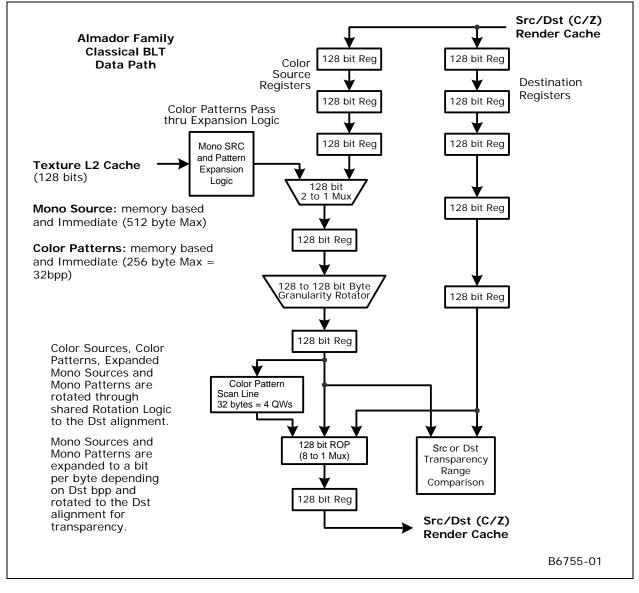

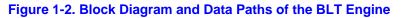

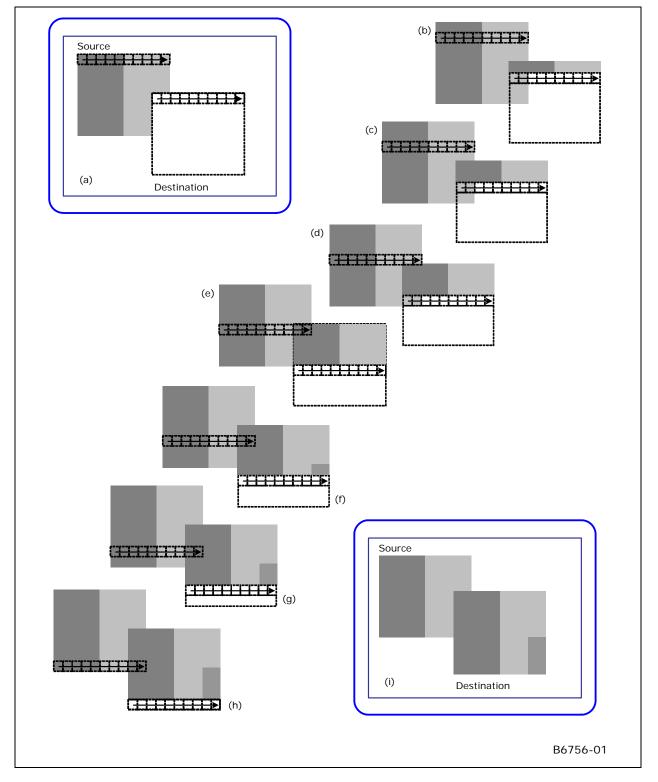

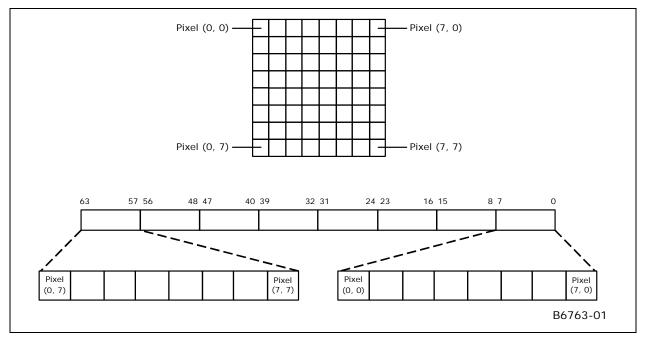

The graphics controller provides a hardware-based BLT engine to off load the work of moving blocks of graphics data from the host CPU. Although the BLT engine is often used simply to copy a block of graphics data from the source to the destination, it also has the ability to perform more complex functions. The BLT engine is capable of receiving three different blocks of graphics data as input as shown in the figure below. The source data may exist in the frame buffer or the Graphics aperture. The pattern data always represents an 8x8 block of pixels that can be located in the frame buffer, Graphics aperture, or passed through a command packet. The pattern data must be located in linear memory. The data already residing at the destination may also be used as an input. The destination data can also be located in the frame buffer or graphics aperture.

#### Figure 1-1. Block Diagram and Data Paths of the BLT Engine

The BLT engine may use any combination of these three different blocks of graphics data as operands, in both bit-wise logical operations to generate the actual data to be written to the destination, and in perpixel write-masking to control the writing of data to the destination. It is intended that the BLT engine will perform these bit-wise and per-pixel operations on color graphics data that is at the same color depth that the rest of the graphics system has been set. However, if either the source or pattern data is monochrome, the BLT engine has the ability to put either block of graphics data through a process called "color expansion" that converts monochrome graphics data to color. Since the destination is often a location in the on-screen portion of the frame buffer, it is assumed that any data already at the destination will be of the appropriate color depth.

# **1.2.1 Basic BLT Functional Considerations**

### 1.2.1.1 Color Depth Configuration and Color Expansion

The graphics system and BLT engine can be configured for color depths of 8, 16, and 32 bits per pixel.

The configuration of the BLT engine for a given color depth dictates the number of bytes of graphics data that the BLT engine will read and write for each pixel while performing a BLT operation. It is assumed that any graphics data already residing at the destination which is used as an input is already at the color depth to which the BLT engine is configured. Similarly, it is assumed that any source or pattern data used as an input has this same color depth, unless one or both is monochrome. If either the source or pattern data is monochrome, the BLT engine performs a process called "color expansion" to convert such monochrome data to color at the color depth to which the BLT engine has been set.

During "color expansion" the individual bits of monochrome source or pattern data that correspond to individual pixels are converted into 1, 2, or 4 bytes (which ever is appropriate for the color depth to which the BLT engine has been set). If a given bit of monochrome source or pattern data carries a value of 1, then the byte(s) of color data resulting from the conversion process are set to carry the value of a specified foreground color. If a given bit of monochrome source or pattern data carries a value of 0, the resulting byte(s) are set to the value of a specified background color or not written if transparency is selected.

The BLT engine is set to a default configuration color depth of 8, 16, or 32 bits per pixel through BLT command packets. Whether the source and pattern data are color or monochrome must be specified using command packets. Foreground and background colors for the color expansion of both monochrome source and pattern data are also specified through the command packets. The source foreground and background colors used in the color expansion of monochrome source data are specified independently of those used for the color expansion of monochrome pattern data.

### 1.2.1.2 Graphics Data Size Limitations

The BLT engine is capable of transferring very large quantities of graphics data. Any graphics data read from and written to the destination is permitted to represent a number of pixels that occupies up to 65,536 scan lines and up to 32,768 bytes per scan line at the destination. The maximum number of pixels that may be represented per scan line's worth of graphics data depends on the color depth.

Any source data used as an input must represent the same number of pixels as is represented by any data read from or written to the destination, and it must be organized so as to occupy the same number of scan lines and pixels per scan line.

The actual number of scan lines and bytes per scan line required to accommodate data read from or written to the destination are set in the destination width & height registers or using X and Y coordinates within the command packets. These two values are essential in the programming of the BLT engine, because the engine uses these two values to determine when a given BLT operation has been completed.

### 1.2.1.3 Bit-Wise Operations

The BLT engine can perform any one of 256 possible bit-wise operations using various combinations of the three previously described blocks of graphics data that the BLT engine can receive as input. These

256 possible bit-wise operations are designed to be compatible with the manner in which raster operations are specified in the standard BLT parameter block, without translation.

The choice of bit-wise operation selects which of the three inputs will be used, as well as the particular logical operation to be performed on corresponding bits from each of the selected inputs. The BLT engine automatically foregoes reading any form of graphics data that has not been specified as an input by the choice of bit-wise operation. An 8-bit code written to the raster operation field of the command packets chooses the bit-wise operation. The following table lists the available bit-wise operations and their corresponding 8-bit codes.

| Code | Value Written to Bits at Destination      |

|------|-------------------------------------------|

| 00   | writes all 0's                            |

| 01   | not( D or ( P or S )))                    |

| 02   | D and ( not( P or S ))                    |

| 03   | not( P or S )                             |

| 04   | S and ( not( D or P ))                    |

| 05   | not( D or P )                             |

| 06   | not( P or ( not( D xor S )))              |

| 07   | not( P or ( D and S ))                    |

| 08   | S and ( D and ( notP ))                   |

| 09   | not( P or ( D xor S ))                    |

| 0A   | D and ( notP )                            |

| 0B   | not( P or ( S and ( notD )))              |

| 0C   | S and ( notP )                            |

| 0D   | not( P or ( D and ( notS )))              |

| 0E   | not( P or ( not( D or S )))               |

| 0F   | notP                                      |

| 10   | P and ( not( D or S ))                    |

| 11   | not( D or S )                             |

| 12   | not( S or ( not( D xor P )))              |

| 13   | not( S or ( D and P ))                    |

| 14   | not( D or ( not( P xor S )))              |

| 15   | not( D or ( P and S ))                    |

| 16   | P xor ( S xor (D and ( not( P and S ))))  |

| 17   | not( S xor (( S xor P ) and ( D xor S ))) |

| 18   | (S xor P) and (P xor D)                   |

| 19   | not( S xor ( D and ( not( P and S ))))    |

| 1A   | P xor ( D or ( S and P ))                 |

| 1B   | not( S xor ( D and ( P xor S )))          |

| 1C   | P xor ( S or ( D and P ))                 |

| 1D   | not( D xor ( S and ( P xor D )))          |

| 1E   | P xor ( D or S )                          |

| 1F   | not( P and ( D or S ))                    |

#### Table 1-1. Bit-Wise Operations and 8-Bit Codes (00-3F)

| CodeValue Written to Bits at Destination20D and (P and (notS))21not(S or(D xor P))22D and (notS)23not(S or (P and (notD)))24(S xor P) and (D xor S)25not(P xor (D and (not(S and P))))26S xor (D or (P and S))27S xor (D or (not(P xor S)))28D and (P xor S)29not(S xor (C or (D or (P and S)))28D and (not(P and S))29not(S xor ((S xor P) and (P xor D)))20S xor (C or (notD))21P xor (S or (notD))22P xor (S or (notD))23not(S xor (D or (notD)))24D and (notS xor (NotP))25not(S or (D and (notP)))30P and (notS)31not(S or (D and (notP)))32S xor (D or (P or S))33notS34S xor (P or (not(D xor S)))35S xor (P or (not(D xor S)))36S xor (D or P)37not(S and (D or P))38P xor (S and (D or P))39S xor (P or (notD))34S xor (P or (notD))35S xor (P or (notD))36N or (P or (notD))37not(S and (P or (notD)))38not(S and (P or (notD)))39S xor (P or (notD))34S xor (P or (notD))35S xor (P or (notD))36N or (P or (notD))37not(S and (P or (notD)))38not(S and (P or (notD)))39 </th <th></th> <th></th>                                                                                                                                                                                                                      |      |                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------|

| 21         not(S or(D xor P))           22         D and (notS)           23         not(S or (P and (notD)))           24         (S xor P) and (D xor S)           25         not(P xor (D and (not(S and P))))           26         S xor (D or (P and S))           27         S xor (D or (not(P xor S)))           28         D and (P xor S)           29         not(S xor (C or (D or (P and S))))           24         D and (not(P and S))           28         D and (not(P and S))           29         not(S xor (C xor P) and (P xor D))))           20         P xor (S xor (notD or S))           21         P xor (S or (notD))           22         S xor (P and (D or S))           20         P xor (S or (notD))           21         P xor (S or (D xor P))           22         P xor (S or (D and (notP)))           30         P and (notS)           31         not(S or (D and (notP)))           32         S xor (P or (D and S))           33         notS           34         S xor (P or (not(D xor S)))           35         S xor (P or (notD xor S)))           36         S xor (P or (notD))           37         not(S and (D or P))                                                      | Code | Value Written to Bits at Destination      |

| 22       D and ( notS )         23       not(S or (P and ( notD )))         24       (S xor P) and (D xor S)         25       not(P xor (D and ( not(S and P ))))         26       S xor (D or ( P and S ))         27       S xor (D or ( not(P xor S )))         28       D and (P xor S)         29       not(P xor (S xor (D or (P and S )))         28       D and ( not(P and S ))         29       not(S xor (( S xor P ) and ( P xor D ))))         20       P xor (S xor (notD or S ))         21       P xor (S or ( notD ))         22       S xor (P and ( D or S ))         20       P xor (S or ( notD ))         21       P xor (S or ( notD ))         22       P xor (S or ( notD ))         24       P and ( notS )         31       not(S or ( D and ( notP )))         32       S xor ( P or ( D and S ))         33       notS         34       S xor ( P or ( not(D xor S )))         35       S xor ( P or ( notD x) S )))         36       S xor ( P or ( notD ))         38       P xor (S and ( D or P ))         39       S xor ( P or ( notD ))         34       S xor ( P or ( notD ))         35       S x                                                                                          | 20   | D and ( P and ( notS ))                   |

| 23         not(S or (P and (notD)))           24         (S xor P) and (D xor S)           25         not(P xor (D and (not(S and P))))           26         S xor (D or (P and S))           27         S xor (D or (not(P xor S)))           28         D and (P xor S)           29         not(S xor (D or (P and S)))           2A         D and (not(P and S))           2B         not(S xor ((S xor P) and (P xor D))))           2C         S xor (P and (D or S))           2D         P xor (S or (notD))           2E         P xor (S or (D xor P))           2F         not(P and (S or (notD)))           30         P and (notS)           31         not(S or (D and (notP)))           32         S xor (P or (P or S))           33         notS           34         S xor (P or (not(D xor S)))           35         S xor (P or (not(D xor S)))           36         S xor (P or (notD P))           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           34         S xor (P or (notD))           35         S xor (P or (notD))           36         P xor (S and (P or (notD))) </td <td>21</td> <td>not( S or( D xor P ))</td> | 21   | not( S or( D xor P ))                     |

| 24         (S xor P) and (D xor S)           25         not(P xor (D and (not(S and P))))           26         S xor (D or (P and S))           27         S xor (D or (not(P xor S)))           28         D and (P xor S)           29         not(P xor (S xor (D or (P and S)))           2A         D and (not(P and S))           2B         not(S xor ((S xor P) and (P xor D)))           2C         S xor (P and (D or S))           2D         P xor (S or (notD))           2E         P xor (S or (D xor P))           2F         not(P and (S or (notD)))           30         P and (notS)           31         not(S or (D and (notP)))           32         S xor (P or (P or S))           33         notS           34         S xor (P or (not(D xor S)))           35         S xor (P or (not(D xor S)))           36         S xor (P or (notD P))           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           34         S xor (P or (notD))           35         S xor (P or (notD))           36         P xor (S and (D or P))           37         not(S and (P or (notD)))<                                               | 22   | D and ( notS )                            |

| 25         not(P xor (D and (not(S and P))))           26         S xor (D or (P and S))           27         S xor (D or (not(P xor S)))           28         D and (P xor S)           29         not(P xor (S xor (D or (P and S))))           2A         D and (not(P and S))           2B         not(S xor ((S xor P) and (P xor D)))           2C         S xor (P and (D or S))           2D         P xor (S or (notD))           2E         P xor (S or (D xor P))           2F         not(P and (S or (notD)))           2F         not(P and (S or (notD)))           30         P and (notS)           31         not(S or (D and (notP)))           32         S xor (D or (P or S))           33         notS           34         S xor (P or (not(D xor S)))           35         S xor (P or (not(D xor S)))           36         S xor (D or P)           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           34         S xor (P or (notD))           35         S xor (P or (notD))           36         P xor (S and (D or P))           37         not(S and (P or (notD)))                                                     | 23   | not( S or ( P and ( notD )))              |

| 26       S xor ( D or ( P and S ))         27       S xor ( D or ( not( P xor S ))))         28       D and ( P xor S )         29       not( P xor ( S xor ( D or ( P and S )))))         2A       D and ( not( P and S ))         2B       not( S xor (( S xor P ) and ( P xor D ))))         2C       S xor ( P and ( D or S ))         2D       P xor ( S or ( notD ))         2E       P xor ( S or ( D xor P ))         2F       not( P and ( S or ( notD )))         30       P and ( notS )         31       not( S or ( D and ( notP )))         32       S xor ( D or ( P or S ))         33       notS         34       S xor ( P or ( not( D xor S )))         35       S xor ( P or ( not( D xor S )))         36       S xor ( D or P )         37       not( S and ( D or P ))         38       P xor ( S and ( D or P ))         39       S xor ( P or ( notD ))         34       S xor ( P or ( notD ))         35       S xor ( P or ( notD ))         36       P xor ( S and ( D or P ))         39       S xor ( P or ( notD ))         34       S xor ( P or ( notD ))         35       S xor ( P or ( notD ))         36 <td>24</td> <td>(S xor P) and (D xor S)</td>                                       | 24   | (S xor P) and (D xor S)                   |

| 27         S xor (D or (not(P xor S)))           28         D and (P xor S)           29         not(P xor (S xor (D or (P and S))))           2A         D and (not(P and S))           2B         not(S xor ((S xor P) and (P xor D)))           2C         S xor (P and (D or S))           2D         P xor (S or (notD))           2E         P xor (S or (D xor P))           2F         not(P and (S or (notD)))           30         P and (notS)           31         not(S or (D and (notP)))           32         S xor (D or (P or S))           33         notS           34         S xor (P or (not(D xor S)))           35         S xor (P or (not(D xor S)))           36         S xor (P or (not(D xor S)))           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           34         S xor (P or (notD))           35         S xor (P or (notD))           38         P xor (S and (D or P))           39         S xor (P or (notD))           34         S xor (P or (notD))           35         S xor (P or (notD))           36         S xor (P or (notD)) <td>25</td> <td>not( P xor ( D and ( not( S and P ))))</td>       | 25   | not( P xor ( D and ( not( S and P ))))    |

| 28         D and (P xor S)           29         not(P xor (S xor (D or (P and S))))           2A         D and (not(P and S))           2B         not(S xor ((S xor P) and (P xor D)))           2C         S xor (P and (D or S))           2D         P xor (S or (notD))           2E         P xor (S or (D xor P))           2F         not(P and (S or (notD)))           30         P and (notS)           31         not(S or (D and (notP)))           32         S xor (D or (P or S))           33         notS           34         S xor (P or (not(D xor S)))           35         S xor (P or (not(D xor S)))           36         S xor (D or P)           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           34         S xor (P or (notD))           35         S xor (P or (notD))           36         P xor (S and (D or P))           37         not(S and (P or (notD)))           38         P xor (S and (P or (notD)))           38         Not (P or (D xor S))           39         S xor (P or (notD)))           38         not(S and (P or (notD)))      <                                                             | 26   | S xor ( D or ( P and S ))                 |

| 29         not(P xor (S xor (D or (P and S))))           2A         D and (not(P and S))           2B         not(S xor ((S xor P) and (P xor D))))           2C         S xor (P and (D or S))           2D         P xor (S or (notD))           2E         P xor (S or (D xor P)))           2F         not(P and (S or (notD)))           30         P and (notS)           31         not(S or (D and (notP))))           32         S xor (D or (P or S))           33         notS           34         S xor (P or (not(D xor S))))           35         S xor (P or (not(D xor S))))           36         S xor (D or P)           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           34         S xor (P or (notD))           35         S xor (P or (notD))           36         P xor (S and (D or P))           37         not(S and (P or (notD)))           38         P xor (S and (P or (notD)))           38         Not (P or (D xor S))           39         S xor (P or (notD)))           30         P xor S                                                                                                                     | 27   | S xor ( D or ( not( P xor S )))           |

| 2A       D and (not(P and S))         2B       not(S xor ((S xor P) and (P xor D)))         2C       S xor (P and (D or S))         2D       P xor (S or (notD))         2E       P xor (S or (D xor P))         2F       not(P and (S or (notD)))         30       P and (notS)         31       not(S or (D and (notP)))         32       S xor (D or (P or S))         33       notS         34       S xor (P or (D and S))         35       S xor (P or (not(D xor S)))         36       S xor (D or P)         37       not(S and (D or P))         38       P xor (S and (D or P))         39       S xor (P or (notD))         34       S xor (P or (notD))         35       S xor (P or (notD))         36       S xor (D or P)         37       not(S and (D or P))         38       P xor (S and (D or P))         39       S xor (P or (notD))         34       S xor (P or (notD))         35       S xor (P or (D xor S))         36       P xor S                                                                                                                                                                                                                                                                  | 28   | D and ( P xor S )                         |

| 2B         not(S xor ((S xor P) and (P xor D)))           2C         S xor (P and (D or S))           2D         P xor (S or (notD))           2E         P xor (S or (D xor P))           2F         not(P and (S or (notD)))           30         P and (notS)           31         not(S or (D and (notP)))           32         S xor (D or (P or S))           33         notS           34         S xor (P or (not(D xor S)))           35         S xor (P or (not(D xor S))))           36         S xor (D or P)           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           3A         S xor (P or (notD))           3B         not(S and (P or (notD)))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29   | not( P xor ( S xor ( D or ( P and S ))))  |

| 2C       S xor (P and (D or S))         2D       P xor (S or (notD))         2E       P xor (S or (D xor P))         2F       not(P and (S or (notD)))         30       P and (notS)         31       not(S or (D and (notP)))         32       S xor (D or (P or S))         33       notS         34       S xor (P or (D and S))         35       S xor (P or (not(D xor S)))         36       S xor (D or P)         37       not(S and (D or P))         38       P xor (S and (D or P))         39       S xor (P or (notD))         3A       S xor (P or (notD))         3B       not(S and (P or (notD)))         3C       P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2A   | D and ( not( P and S ))                   |

| 2D         P xor (S or (notD))           2E         P xor (S or (D xor P))           2F         not(P and (S or (notD)))           30         P and (notS)           31         not(S or (D and (notP)))           32         S xor (D or (P or S))           33         notS           34         S xor (P or (D and S))           35         S xor (P or (not(D xor S)))           36         S xor (D or P)           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           3A         S xor (P or (notD))           3B         not(S and (P or (notD)))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2B   | not( S xor (( S xor P ) and ( P xor D ))) |

| 2E         P xor (S or (D xor P))           2F         not(P and (S or (notD)))           30         P and (notS)           31         not(S or (D and (notP)))           32         S xor (D or (P or S))           33         notS           34         S xor (P or (D and S))           35         S xor (P or (not(D xor S)))           36         S xor (D or P)           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           3A         S xor (P or (notD))           3B         not(S and (P or (notD)))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2C   | S xor ( P and ( D or S ))                 |

| 2F         not(P and (S or (notD)))           30         P and (notS)           31         not(S or (D and (notP)))           32         S xor (D or (P or S))           33         notS           34         S xor (P or (D and S))           35         S xor (P or (not(D xor S)))           36         S xor (D or P)           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           3A         S xor (P or (notD))           3B         not(S and (P or (notD)))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2D   | P xor ( S or ( notD ))                    |

| 30         P and (notS)           31         not(S or (D and (notP)))           32         S xor (D or (P or S))           33         notS           34         S xor (P or (D and S))           35         S xor (P or (not(D xor S)))           36         S xor (D or P)           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           3A         S xor (P or (notD))           3B         not(S and (P or (notD)))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2E   | P xor ( S or ( D xor P ))                 |

| 31         not(S or (D and (notP)))           32         S xor (D or (P or S))           33         notS           34         S xor (P or (D and S))           35         S xor (P or (not(D xor S)))           36         S xor (D or P)           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           3A         S xor (P or (notD))           3B         not(S and (P or (notD)))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2F   | not( P and ( S or ( notD )))              |

| 32       S xor (D or (P or S))         33       notS         34       S xor (P or (D and S))         35       S xor (P or (not(D xor S)))         36       S xor (D or P)         37       not(S and (D or P))         38       P xor (S and (D or P))         39       S xor (P or (notD))         3A       S xor (P or (notD))         3B       not(S and (P or (notD)))         3C       P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30   | , , ,                                     |

| 33         notS           34         S xor (P or (D and S))           35         S xor (P or (not(D xor S)))           36         S xor (D or P)           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           3A         S xor (P or (notD))           3B         not(S and (P or (notD)))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31   | not( S or ( D and ( notP )))              |

| 34         S xor (P or (D and S))           35         S xor (P or (not(D xor S)))           36         S xor (D or P)           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           3A         S xor (P or (notD))           3B         not(S and (P or (notD)))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32   | S xor ( D or ( P or S ))                  |

| 35         S xor (P or (not(D xor S)))           36         S xor (D or P)           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           3A         S xor (P or (notD xor S))           3B         not(S and (P or (notD)))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33   | notS                                      |

| 36         S xor (D or P)           37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           3A         S xor (P or (notD))           3B         not(S and (P or (notD)))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34   | S xor ( P or ( D and S ))                 |

| 37         not(S and (D or P))           38         P xor (S and (D or P))           39         S xor (P or (notD))           3A         S xor (P or (notD))           3B         not(S and (P or (notD)))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35   | S xor ( P or ( not( D xor S )))           |

| 38         P xor (S and (D or P))           39         S xor (P or (notD))           3A         S xor (P or (D xor S))           3B         not(S and (P or (notD)))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 36   | S xor ( D or P )                          |

| 39         S xor (P or (notD))           3A         S xor (P or (D xor S))           3B         not(S and (P or (notD)))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37   | not( S and ( D or P ))                    |

| 3A         S xor (P or (D xor S))           3B         not(S and (P or (notD)))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38   |                                           |

| 3B         not( S and ( P or ( notD )))           3C         P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39   | S xor ( P or ( notD ))                    |

| 3C P xor S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3A   | S xor ( P or ( D xor S ))                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3B   | not( S and ( P or ( notD )))              |

| 3D S xor ( P or ( not( D or S )))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3C   |                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3D   | S xor ( P or ( not( D or S )))            |

| 3E S xor ( P or ( D and ( notS )))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3E   | S xor ( P or ( D and ( notS )))           |

| 3F not( P and S )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3F   | not( P and S )                            |

Notes: S = Source Data

P = Pattern Data

D = Data Already Existing at the Destination

| Code | Value Written to Bits at Destination     |

|------|------------------------------------------|

| 40   | P and ( S and ( notD ))                  |

| 41   | not( D or ( P xor S ))                   |

| 42   | (S xor D) and (P xor D)                  |

| 43   | not( S xor ( P and ( not( D and S ))))   |

| 44   | S and ( notD )                           |

| 45   | not( D or ( P and ( notS )))             |

| 46   | D xor ( S or ( P and D ))                |

| 47   | not( P xor ( S and ( D xor P )))         |

| 48   | S and ( D xor P )                        |

| 49   | not( P xor ( D xor ( S or ( P and D )))) |

| 4A   | D xor ( P and ( S or D ))                |

| 4B   | P xor ( D or ( notS ))                   |

| 4C   | S and ( not( D and P ))                  |

| 4D   | not( S xor (( S xor P ) or ( D xor S ))) |

| 4E   | P xor ( D or ( S xor P ))                |

| 4F   | not( P and ( D or ( notS )))             |

| 50   | P and ( notD )                           |

| 51   | not( D or ( S and ( notP )))             |

| 52   | D xor (P or ( S and D ))                 |

| 53   | not( S xor ( P and ( D xor S )))         |

| 54   | not( D or ( not( P or S )))              |

| 55   | notD                                     |

| 56   | D xor ( P or S )                         |

| 57   | not( D and ( P or S ))                   |

| 58   | P xor ( D and ( S or P ))                |

| 59   | D xor ( P or ( notS ))                   |

| 5A   | D xor P                                  |

| 5B   | D xor ( P or ( not( S or D )))           |

| 5C   | D xor ( P or ( S xor D ))                |

| 5D   | not( D and ( P or ( notS )))             |

| 5E   | D xor ( P or ( S and ( notD )))          |

| 5F   | not( D and P )                           |

### Table 1-2. Bit-Wise Operations and 8-bit Codes (40 - 7F)

| Code | Value Written to Bits at Destination             |

|------|--------------------------------------------------|

| 60   | P and (D xor S)                                  |

| 61   | not( D xor ( S xor ( P or ( D and S ))))         |

| 62   | D xor ( S and ( P or D ))                        |

| 63   | S xor ( D or ( notP ))                           |

| 64   | S xor ( D and ( P or S ))                        |

| 65   | D xor ( S or ( notP ))                           |

| 66   | D xor S                                          |

| 67   | S xor ( D or ( not( P or S )))                   |

| 68   | not( D xor ( S xor ( P or ( not( D or S<br>))))) |

| 69   | not( P xor ( D xor S ))                          |

| 6A   | D xor ( P and S )                                |

| 6B   | not( P xor ( S xor ( D and ( P or S ))))         |

| 6C   | S xor ( D and P )                                |

| 6D   | not( P xor ( D xor ( S and ( P or D ))))         |

| 6E   | S xor ( D and ( P or ( notS )))                  |

| 6F   | not( P and ( not( D xor S )))                    |

| 70   | P and ( not( D and S ))                          |

| 71   | not( S xor (( S xor D ) and ( P xor D )))        |

| 72   | S xor ( D or ( P xor S ))                        |

| 73   | not( S and ( D or ( notP )))                     |

| 74   | D xor ( S or ( P xor D ))                        |

| 75   | not( D and ( S or ( notP )))                     |

| 76   | S xor ( D or ( P and ( notS )))                  |

| 77   | not( D and S )                                   |

| 78   | P xor ( D and S )                                |

| 79   | not( D xor ( S xor ( P and ( D or S ))))         |

| 7A   | D xor ( P and ( S or ( notD )))                  |

| 7B   | not( S and ( not( D xor P )))                    |

| 7C   | S xor ( P and ( D or ( notS )))                  |

| 7D   | not( D and ( not( P xor S )))                    |

| 7E   | (S xor P) or (D xor S)                           |

| 7F   | not( D and ( P and S ))                          |

Notes: S = Source Data P = Pattern Data D = Data Already Existing at the Destination

### Table 1-3. Bit-Wise Operations and 8-bit Codes (80 - BF)

| Code | Value Written to Bits at Destination    |

|------|-----------------------------------------|

| 80   | D and ( P and S )                       |

| 81   | not(( S xor P ) or ( D xor S ))         |

| 82   | D and ( not( P xor S ))                 |

| 83   | not( S xor ( P and ( D or ( notS ))))   |

| 84   | S and ( not( D xor P ))                 |

| 85   | not( P xor ( D and ( S or ( notP ))))   |

| 86   | D xor ( S xor ( P and ( D or S )))      |

| 87   | not( P xor ( D and S ))                 |

| 88   | D and S                                 |

| 89   | not( S xor ( D or ( P and ( notS ))))   |

| 8A   | D and ( S or ( notP ))                  |

| 8B   | not( D xor ( S or ( P xor D )))         |

| 8C   | S and ( D or ( notP ))                  |

| 8D   | not( S xor ( D or ( P xor S )))         |

| 8E   | S xor (( S xor D ) and ( P xor D ))     |

| 8F   | not( P and ( not( D and S )))           |

| 90   | P and ( not( D xor S ))                 |

| 91   | not( S xor ( D and ( P or ( notS ))))   |

| 92   | D xor ( P xor ( S and ( D or P )))      |

| 93   | not( S xor ( P and D ))                 |

| 94   | P xor ( S xor ( D and ( P or S )))      |

| 95   | not( D xor ( P and S ))                 |

| 96   | D xor ( P xor S )                       |

| 97   | P xor ( S xor ( D or ( not( P or S )))) |

| 98   | not( S xor ( D or ( not( P or S ))))    |

| 99   | not( D xor S )                          |

| 9A   | D xor ( P and ( notS ))                 |

| 9B   | not( S xor ( D and ( P or S )))         |

| 9C   | S xor ( P and ( notD ))                 |

| 9D   | not( D xor ( S and ( P or D )))         |

| 9E   | D xor ( S xor ( P or ( D and S )))      |

| 9F   | not( P and ( D xor S ))                 |

| Code | Value Written to Bits at Destination  |

|------|---------------------------------------|

| A0   | D and P                               |

| A1   | not( P xor ( D or ( S and ( notP )))) |

| A2   | D and ( P or ( notS ))                |

| A3   | not( D xor ( P or ( S xor D )))       |

| A4   | not( P xor ( D or ( not( S or P ))))  |

| A5   | not( P xor D )                        |

| A6   | D xor ( S and ( notP ))               |

| A7   | not( P xor ( D and ( S or P )))       |

| A8   | D and ( P or S )                      |

| A9   | not( D xor ( P or S ))                |

| AA   | D                                     |

| AB   | D or ( not( P or S))                  |

| AC   | S xor (P and ( D xor S ))             |

| AD   | not( D xor ( P or ( S and D )))       |

| AE   | D or ( S and ( notP ))                |

| AF   | D or ( notP )                         |

| B0   | P and ( D or ( notS ))                |

| B1   | not( P xor ( D or ( S xor P )))       |

| B2   | S xor (( S xor P ) or ( D xor S ))    |

| B3   | not( S and ( not( D and P )))         |

| B4   | P xor ( S and ( notD ))               |

| B5   | not( D xor ( P and ( S or D )))       |

| B6   | D xor ( P xor ( S or ( D and P )))    |

| B7   | not( S and ( D xor P ))               |

| B8   | P xor ( S and ( D xor P ))            |

| B9   | not( D xor ( S or ( P and D )))       |

| BA   | D or ( P and ( notS ))                |

| BB   | D or ( notS )                         |

| BC   | S xor ( P and ( not( D and S )))      |

| BD   | not(( S xor D ) and ( P xor D ))      |

| BE   | D or ( P xor S )                      |

| BF   | D or ( not( P and S ))                |

**Notes:** S = Source Data

P = Pattern Data D = Data Already Existing at the Destination

| Code | Value Written to Bits at Destination  |

|------|---------------------------------------|

| C0   | P and S                               |

| C1   | not( S xor ( P or ( D and ( notS )))) |

| C2   | not( S xor ( P or ( not( D or S ))))  |

| C3   | not( P xor S )                        |

| C4   | S and ( P or ( notD ))                |

| C5   | not( S xor ( P or ( D xor S )))       |

| C6   | S xor ( D and ( notP ))               |

| C7   | not( P xor ( S and ( D or P )))       |

| C8   | S and ( D or P )                      |

| C9   | not( S xor ( P or D ))                |

| CA   | D xor ( P and ( S xor D ))            |

| СВ   | not( S xor ( P or ( D and S )))       |

| CC   | S                                     |

| CD   | S or ( not( D or P ))                 |

| CE   | S or ( D and ( notP ))                |

| CF   | S or ( notP )                         |

| D0   | P and ( S or ( notD ))                |

| D1   | not( P xor ( S or ( D xor P )))       |

| D2   | P xor ( D and ( notS ))               |

| D3   | not( S xor ( P and ( D or S )))       |

| D4   | S xor (( S xor P ) and ( P xor D ))   |

| D5   | not( D and ( not( P and S )))         |

| D6   | P xor ( S xor ( D or ( P and S )))    |

| D7   | not( D and ( P xor S ))               |

| D8   | P xor ( D and ( S xor P ))            |

| D9   | not( S xor ( D or ( P and S )))       |

| DA   | D xor ( P and ( not( S and D )))      |

| DB   | not(( S xor P ) and ( D xor S ))      |

| DC   | S or ( P and ( notD ))                |

| DD   | S or ( notD )                         |

| DE   | S or ( D xor P )                      |

| DF   | S or ( not( D and P ))                |

### Table 1-4. Bit-Wise Operations and 8-bit Codes (C0 - FF)

| Code | Value Written to Bits at Destination            |

|------|-------------------------------------------------|

| E0   | P and ( D or S )                                |

| E1   | not( P xor ( D or S ))                          |

| E2   | D xor ( S and ( P xor D ))                      |

| E3   | not( P xor ( S or ( D and P )))                 |

| E4   | S xor ( D and ( P xor S ))                      |

| E5   | not( P xor ( D or ( S and P )))                 |

| E6   | S xor ( D and ( not( P and S )))                |

| E7   | not(( S xor P ) and ( P xor D ))                |

| E8   | S xor (( S xor P ) and ( D xor S ))             |

| E9   | not( D xor ( S xor ( P and ( not( D and S ))))) |

| EA   | D or ( P and S )                                |

| EB   | D or ( not( P xor S ))                          |

| EC   | S or ( D and P )                                |

| ED   | S or ( not( D xor P ))                          |

| EE   | D or S                                          |

| EF   | S or ( D or ( notP ))                           |

| F0   | Р                                               |

| F1   | P or ( not( D or S ))                           |

| F2   | P or ( D and ( notS ))                          |

| F3   | P or ( notS )                                   |

| F4   | P or ( S and ( notD ))                          |

| F5   | P or ( notD )                                   |

| F6   | P or ( D xor S )                                |

| F7   | P or ( not( D and S ))                          |

| F8   | P or ( D and S )                                |

| F9   | P or ( not( D xor S ))                          |

| FA   | D or P                                          |

| FB   | D or ( P or ( notS ))                           |

| FC   | P or S                                          |

| FD   | P or ( S or ( notD ))                           |

| FE   | D or ( P or S )                                 |

| FF   | writes all 1's                                  |

|      |                                                 |

Notes: S = Source Data

P = Pattern Data D = Data Already Existing at the Destination

### 1.2.1.4 Per-Pixel Write-Masking Operations

The BLT engine is able to perform per-pixel write-masking with various data sources used as pixel masks to constrain which pixels at the destination are to be written to by the BLT engine. As shown in the figure below, either monochrome source or monochrome pattern data may be used as pixel masks. Color pattern data cannot be used. Another available pixel mask is derived by comparing a particular color range per color channel to either the color already specified for a given pixel at the destination or source.

The command packets can specify the monochrome source or the monochrome pattern data as a pixel mask. When this feature is used, the bits that carry a value of 0 cause the bytes of the corresponding pixel at the destination to not be written to by the BLT engine, thereby preserving whatever data was originally carried within those bytes. This feature can be used in writing characters to the display, while also preserving the pre-existing backgrounds behind those characters. When both operands are in the transparent mode, the logical AND of the 2 operands are used for the write enables per pixel.

The 3-bit field, destination transparency mode, within the command packets can select per-pixel writemasking with a mask based on the results of color comparisons. The monochrome source background and foreground are range compared with either the bytes for the pixels at the destination or the source operand. This operation is described in the BLT command packet and register descriptions.

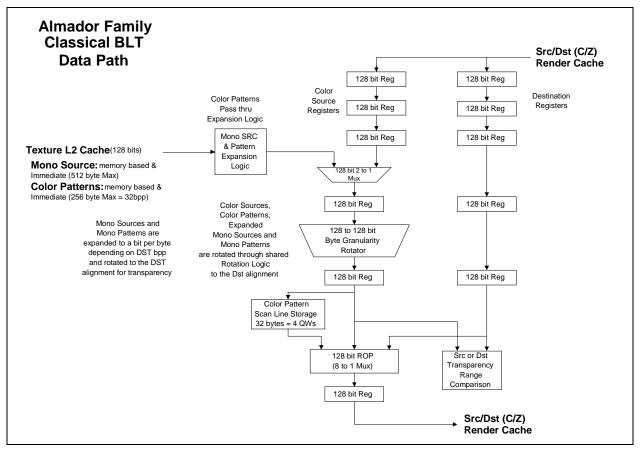

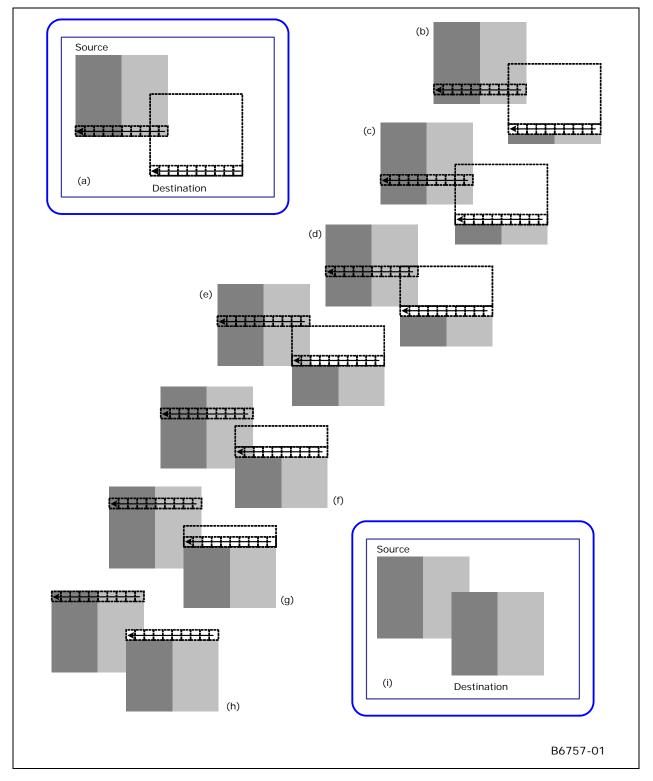

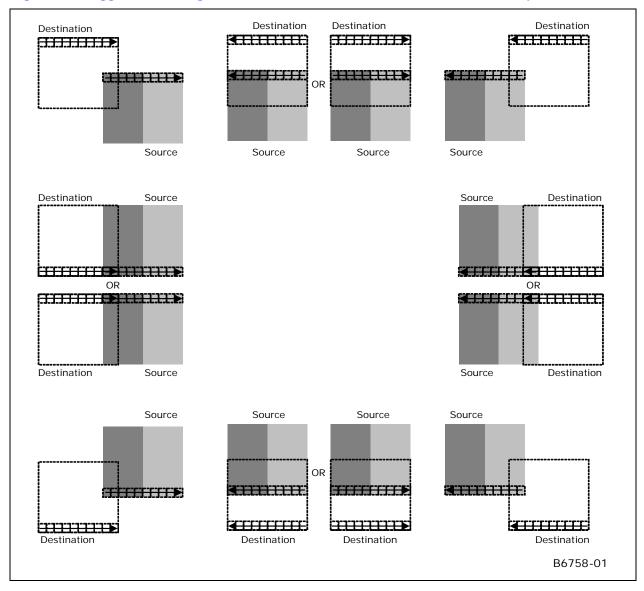

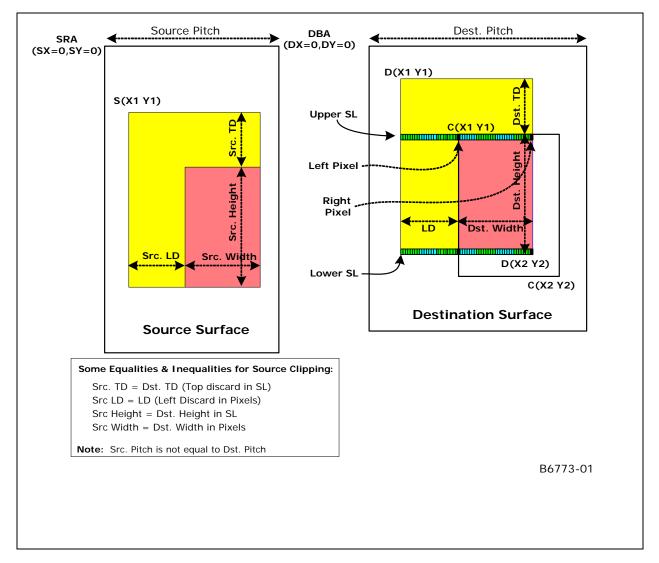

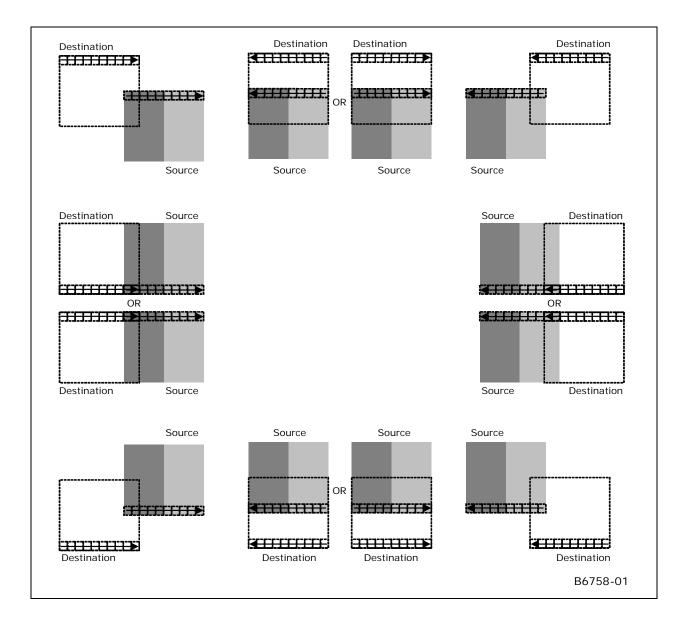

### 1.2.1.5 When the Source and Destination Locations Overlap

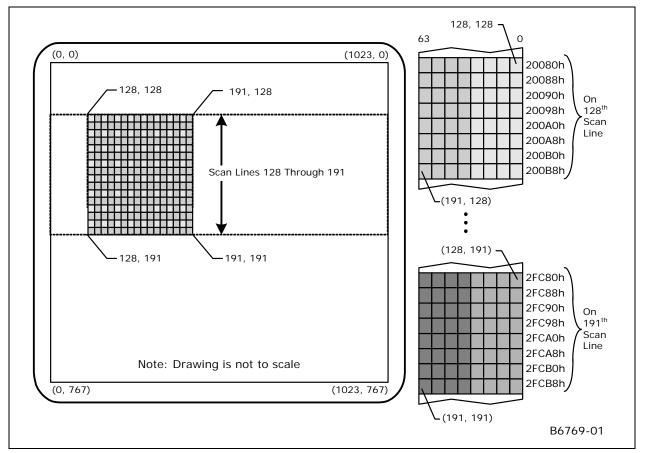

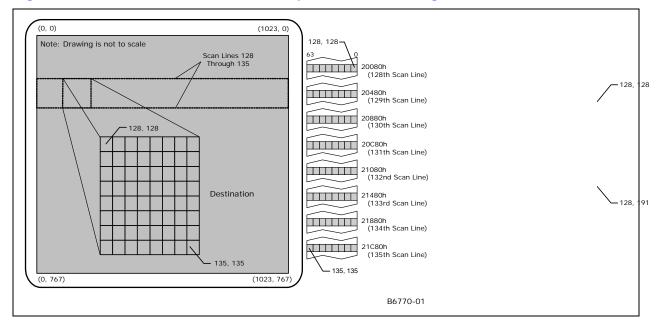

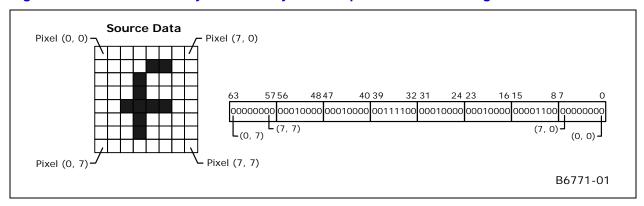

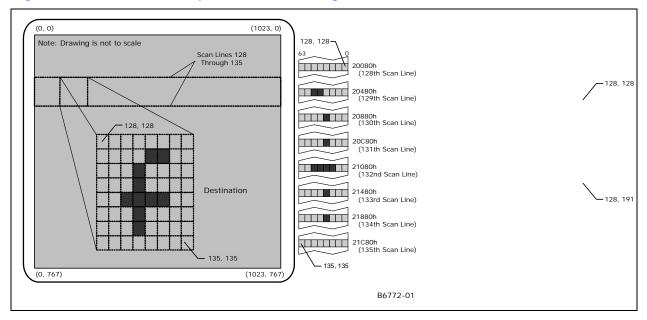

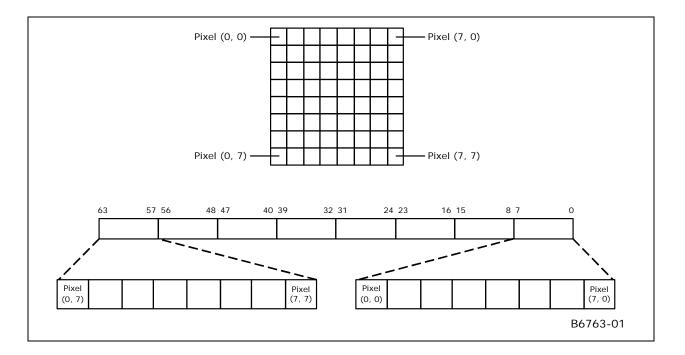

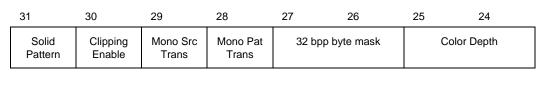

It is possible to have BLT operations in which the locations of the source and destination data overlap. This frequently occurs in BLT operations where a user is shifting the position of a graphical item on the display by only a few pixels. In these situations, the BLT engine must be programmed so that destination data is not written into destination locations that overlap with source locations before the source data at those locations has been read. Otherwise, the source data will become corrupted. The XY commands determine whether there is an overlap and perform the accesses in the proper direction to avoid data corruption.