# Intel<sup>®</sup> OpenSource HD Graphics Programmer's Reference Manual (PRM) Volume 3 Part 2: Display Registers – CPU Registers (SandyBridge)

# For the 2011 Intel Core Processor Family

May 2011 Revision 1.0

#### NOTICE:

This document contains information on products in the design phase of development, and Intel reserves the right to add or remove product features at any time, with or without changes to this open source documentation.

#### **Creative Commons License**

You are free to Share — to copy, distribute, display, and perform the work

#### Under the following conditions:

**Attribution**. You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

No Derivative Works. You may not alter, transform, or build upon this work.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The SandyBridge chipset family, Havendale/Auburndale chipset family, Intel<sup>®</sup> 965 Express Chipset Family, Intel<sup>®</sup> G35 Express Chipset, and Intel<sup>®</sup> 965GMx Chipset Mobile Family Graphics Controller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel<sup>®</sup> sales office or your distributor to obtain the latest specifications and before placing your product order. I2C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I2C bus/protocol and was developed by Intel<sup>®</sup>. Implementations of the I2C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2011, Intel Corporation. All rights reserved.

# Contents

| 1. CPU Display Registers [DevSNB+]                                                                               | 7  |

|------------------------------------------------------------------------------------------------------------------|----|

| 1.1 1.1 Introduction and Register Summary                                                                        | 7  |

| 1.1.1 Terminology                                                                                                |    |

| 1.1.2 Display Mode Set Sequence                                                                                  |    |

| 2. North Shared Functions (40000h–4FFFFh)                                                                        | 11 |

| 2.1 VGA Control Registers                                                                                        | 11 |

| 2.2 Sine ROM Registers                                                                                           |    |

| 2.2.1 2.4.1 SINE_ROM—Sine ROM                                                                                    | 15 |

| 2.3 Power Measurement Registers                                                                                  |    |

| 2.3.1 DE_POWER1 – Display Engine Power Register 1                                                                | 16 |

| 2.3.2 DE_POWER2 – Display Engine Power Register 2                                                                | 17 |

| 2.4 DPFC Control Registers (43200h–433FFh)                                                                       |    |

| 2.4.1 DPFC_CB_BASE – DPFC Compressed Buffer Base Address                                                         |    |

| 2.4.2 DPFC_CONTROL— DPFC Control                                                                                 |    |

| 2.4.3 DPFC_RECOMP_CTL — DPFC ReComp Control                                                                      |    |

| 2.4.4 DPFC_STATUS — DPFC Status                                                                                  |    |

| 2.4.5 DPFC_CPU_Fence_Offset — Y Offset CPU Fence Base to Display Buffer Base                                     |    |

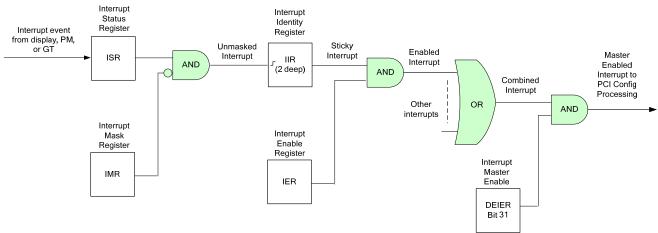

| 2.5 Interrupt Control Registers                                                                                  |    |

| 2.5.1 Display Engine Interrupt Registers Bit Definition                                                          |    |

| 2.5.2 DEISR — Display Engine Interrupt Status Register                                                           |    |

| 2.5.3 DEIMR — Display Engine Interrupt Mask Register                                                             |    |

| 2.5.4 DEIIR — Display Engine Interrupt Identity Register                                                         |    |

| 2.5.5 DEIER — Display Engine Interrupt Enable Register                                                           |    |

| 2.5.6 GT Interrupt Registers Bit Definition                                                                      |    |

| <ul> <li>2.5.7 GTISR — GT Interrupt Status Register</li> <li>2.5.8 GTIMR — GT Interrupt Mask Register</li> </ul> |    |

| 2.5.9 GTIR — GT Interrupt Identity Register                                                                      |    |

| 2.5.9 GTIR — GT Interrupt Leable Register                                                                        |    |

| 2.5.10 Power Management Interrupt Registers Bit Definition [DevSNB]                                              |    |

| 2.5.12 PMISR — PM Interrupt Status Register                                                                      |    |

| 2.5.13 PMIMR — Power Management Interrupt Mask Register                                                          |    |

| 2.5.14 PMIIR — Power Management Interrupt Identity Register                                                      |    |

| 2.5.15 PMIER — Power Management Interrupt Enable Register                                                        |    |

| 2.5.16 Digital Port Hot Plug Control Register                                                                    |    |

| 2.5.17 GTT Fault Status Register                                                                                 |    |

| 2.6 Display Engine Render Response                                                                               |    |

| 2.6.1 Display Engine Render Response Message Bit Definition                                                      |    |

| 2.6.2 DERRMR – Display Engine Render Response Mask Register                                                      |    |

| 2.7 Display Arbitration Control                                                                                  | 47 |

| 2.7.1 DISP ARB CTL—Display Arbiter Control                                                                       | 47 |

| 2.7.2 DISP_ARB_CTL2—Display Arbiter Control 2 [DevSNB]                                                           | 49 |

| 2.8 Display Watermark Registers                                                                                  |    |

| 2.8.1 WM0_PIPE_A—Pipe A Main Watermarks                                                                          |    |

| 2.8.2 WM0_PIPE_B—Pipe B Main Watermarks                                                                          |    |

| 2.8.3 WM1—Low Power 1 Display Watermarks                                                                         |    |

| 2.8.4 WM2—Low Power 2 Display Watermarks                                                                         |    |

| 2.8.5 WM3—Low Power 3 Display Watermarks                                                                         |    |

| 2.8.6 WM1S—Low Power 1 Sprite Watermark                                                                          |    |

| 2.9 Backlight Control and Modulation Histogram Registers                                                         | 56 |

| 2.9.1           | BLC_PWM_CTL2—Backlight PWM Control Register 2                                            |      |

|-----------------|------------------------------------------------------------------------------------------|------|

| 2.9.2           | BLC_PWM_CTL—Backlight PWM Control Register                                               |      |

| 2.9.3           | BLM_HIST_CTL—Image Enhancement Histogram Control Register                                |      |

| 2.9.4           | Image Enhancement Bin Data Register                                                      |      |

| 2.9.5           | Histogram Threshold Guardband Register                                                   |      |

|                 | otion Blur Mitigation (MBM) Control                                                      |      |

| 2.10.1          | MBM_CTRL—MBM Control                                                                     |      |

| 2.10.2          | MBM_TBL—MBM Overdrive Table                                                              |      |

|                 | olor Conversion and Control Registers                                                    |      |

| 2.11.1          | Pipe A Color Control                                                                     |      |

| 2.11.2          | Pipe B Color Control                                                                     |      |

|                 | splay Palette Registers (4A000h-4CFFFh)                                                  |      |

| 2.12.1          | LGC_PALETTE_A—Pipe A Legacy Display Palette                                              |      |

| 2.12.2          | LGC_PALETTE_B—Pipe B Legacy Display Palette                                              |      |

| 2.12.3          | PREC_PALETTE_A—Pipe A Precision Display Palette                                          |      |

| 2.12.4          | PREC_PALETTE_B—Pipe B Precision Display Palette                                          |      |

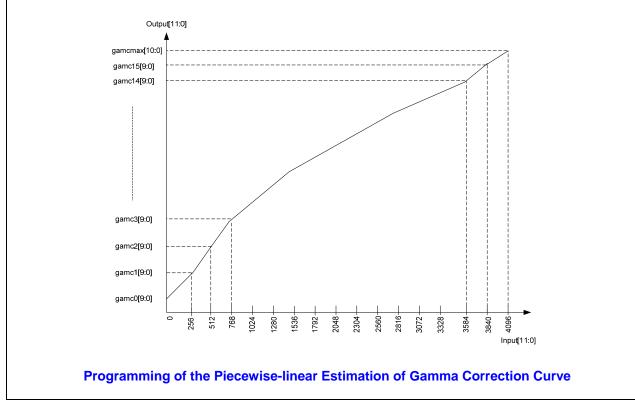

| 2.12.5          | PIPEAGCMAX—Pipe A Gamma Correction Max                                                   |      |

| 2.12.6          | PIPEBGCMAX — Pipe B Gamma Correction Max                                                 |      |

|                 | oftware Flag Registers (4F000h–4F10Fh)                                                   |      |

| 2.13.1          | Software Flag Registers                                                                  |      |

| 2.13.2          | DE_LOAD_SL — Display Load Scan Lines                                                     |      |

|                 | h Pipe and Port Controls (60000h–6FFFh)                                                  |      |

|                 | e A Timing                                                                               |      |

| 3.1.1           | HTOTAL_A—Pipe A Horizontal Total Register                                                |      |

| 3.1.2           | HBLANK_A—Pipe A Horizontal Blank Register                                                |      |

| 3.1.3           | HSYNC_A—Pipe A Horizontal Sync Register                                                  |      |

| 3.1.4           | VTOTAL_A—Pipe A Vertical Total Register                                                  |      |

| 3.1.5           | VBLANK_A—Pipe A Vertical Blank Register                                                  |      |

| 3.1.6           | VSYNC_A—Pipe A Vertical Sync Register                                                    |      |

| 3.1.7           | PIPEASRC—Pipe A Source Image Size                                                        | . 99 |

| 3.1.8           | VSYNCSHIFT_A— Vertical Sync Shift Register                                               |      |

| 3.1.9           | Pipe A M/N Values                                                                        |      |

|                 | e B Timing                                                                               |      |

|                 | HTOTAL_B—Pipe B Horizontal Total Register                                                |      |

|                 | HBLANK_B—Pipe B Horizontal Blank Register                                                |      |

| 3.2.3           | HSYNC_B—Pipe B Horizontal Sync Register                                                  |      |

| 3.2.4           | VTOTAL_B—Pipe B Vertical Total Register                                                  |      |

| 3.2.5           | VBLANK_B—Pipe B Vertical Blank Register                                                  |      |

| 3.2.6           | VSYNC_B—Pipe B Vertical Sync Register                                                    | 111  |

|                 | PIPEBSRC—Pipe B Source Image Size                                                        |      |

| 3.2.8           | VSYNCSHIFT_B— Vertical Sync Shift Register                                               |      |

|                 | e B M/N Values                                                                           |      |

| 3.3.1           | PipeBDataM1— Pipe B Data M value 1                                                       |      |

| 3.3.2           | PipeBDataN1— Pipe B Data N value 1                                                       |      |

| 3.3.3           | PipeBDataM2— Pipe B Data M value 2                                                       |      |

| 3.3.4           | PipeBDataN2— Pipe B Data N value 2                                                       |      |

| 3.3.5           | PipeBDPLinkM1— Pipe B Link M value 1                                                     |      |

| 3.3.6           | PipeBDPLinkN1— Pipe B Link N value 1                                                     |      |

| 3.3.7<br>3.3.8  | PipeBDPLinkM2— Pipe B Link M value 2                                                     |      |

|                 | PipeBDPLinkN2— Pipe B Link N value 2                                                     |      |

| 3.4 Em<br>3.4.1 | DP_A—DisplayPort A Control Register                                                      |      |

| 3.4.1           | DP_A—DisplayPort A Control Register<br>DPA_AUX_CH_CTL—Display Port A AUX Channel Control | 171  |

| 3.4.Z           |                                                                                          | 121  |

| 3.4.3 DPA_AUX_CH_DATA1—Display Port A AUX Data Register 1                       | 123 |

|---------------------------------------------------------------------------------|-----|

| 3.4.4 DPA_AUX_CH_DATA2—Display Port A AUX Data Register 2                       |     |

| 3.4.5 DPA_AUX_CH_DATA3—Display Port A AUX Data Register 3                       |     |

| 3.4.6 DPA_AUX_CH_DATA4—Display Port A AUX Data Register 4                       |     |

| 3.4.7 DPA_AUX_CH_DATA5—Display Port A AUX Data Register 5                       |     |

| 3.5 Panel Fitter Control Registers                                              |     |

| 3.5.1 PF WIN POS—Panel Fitter Window Position                                   | 125 |

| 3.5.2 PF_WIN_SZ—Panel Fitter Window Size                                        |     |

| 3.5.3 PF CTRL 1—Panel Fitter Control 1                                          |     |

| 3.5.4 Panel Fitter Coefficient Registers.                                       |     |

| 3.6 Panel Fitter Horizontal Coefficients                                        |     |

| 3.6.1 PF_HFILTL_COEF—Panel Fitter Horizontal Luma/Red Coefficients              |     |

| 3.6.2 PF HFILTC COEF—Panel Fitter Horizontal Chroma/Green and Blue Coefficients |     |

| 3.7 Panel Fitter Vertical Coefficients                                          |     |

| 3.7.1 PF_VFILTL_COEF—Panel Fitter Vertical Luma/Red Coefficients                |     |

| 3.7.2 PF_VFILTC_COEF—Panel Fitter Vertical Chroma/Green and Blue Coefficients   |     |

| 4. Plane Controls (7000h–7FFFh)                                                 |     |

|                                                                                 |     |

| 4.1 Display Pipeline A                                                          |     |

| 4.1.1 PIPEA_DSL—Pipe A Display Scan Line                                        |     |

| 4.1.2 PIPEA_SLC—Pipe A Display Scan Line Count Range Compare                    |     |

| 4.1.3 PIPEACONF—Pipe A Configuration Register                                   |     |

| 4.2 Display Pipeline A Counters and Timestamps                                  |     |

| 4.2.1 PIPEA_FRMCOUNT—Pipe A Frame Counter                                       |     |

| 4.2.2 PIPEA_FLIPCOUNT—Pipe A Flip Counter                                       |     |

| 4.2.3 PIPEA_FRMTIMESTAMP—Pipe A Frame Time Stamp                                | 145 |

| 4.2.4 PIPEA_FLIPTIMESTAMP—Pipe A Flip Time Stamp                                | 145 |

| 4.3 Display Timestamp                                                           |     |

| 4.3.1 TIMESTAMP_HI—Time Stamp High Value                                        |     |

| 4.4 Display Pipeline B                                                          |     |

| 4.4.1 PIPEB_DSL—Pipe B Display Scan Line                                        |     |

| 4.4.2 PIPEB_SLC—Pipe B Display Scan Line Count Range Compare                    |     |

| 4.4.3 PIPEBCONF—Pipe B Configuration Register                                   |     |

| 4.5 Display Pipeline B Counters and Timestamps                                  |     |

| 4.5.1 PIPEB_FRMCOUNT—Pipe B Frame Counter                                       |     |

| 4.5.2 PIPEB_FLIPCOUNT—Pipe B Flip Counter                                       |     |

| 4.5.3 PIPEB_FRMTIMESTAMP—Pipe B Frame Time Stamp                                |     |

| 4.5.4 PIPEB_FLIPTIMESTAMP—Pipe B Flip Time Stamp                                |     |

| 4.6 Cursor A Plane Control Registers                                            |     |

| 4.6.1 CURACNTR—Cursor A Control Register                                        |     |

| 4.6.2 CURABASE—Cursor A Base Address Register                                   |     |

| 4.6.3 CURAPOS—Cursor A Position Register                                        |     |

| 4.6.4 CURAVGAPOPUPBASE—Cursor A VGA Popup Base Address Register                 |     |

| 4.6.5 CURAPALET—Cursor A Palette registers                                      |     |

| 4.6.6 CURASURFLIVE—Cursor A Live Surface Base Address                           | 162 |

| 4.7 Cursor B Plane Control Registers                                            | 162 |

| 4.7.1 CURBCNTR—Cursor B Control Register                                        |     |

| 4.7.2 CURBBASE—Cursor B Base Address Register                                   | 164 |

| 4.7.3 CURBPOS—Cursor B Position Register                                        | 165 |

| 4.7.4 CURBPALET—Cursor B Palette registers                                      |     |

| 4.7.5 CURBSURFLIVE—Cursor B Live Surface Base Address Register                  | 166 |

| 4.8 Primary A Plane Control                                                     | 167 |

| 4.8.2 DSPALINOFF—Primary A Linear Offset Register                               | 170 |

| 4.8.3 DSPASTRIDE—Primary A Stride Register                                      | 171 |

|                                                                                 |     |

| 4.8.4   | DSPASURF—Primary A Surface Base Address Register          |     |

|---------|-----------------------------------------------------------|-----|

|         | DSPATILEOFF—Primary A Tiled Offset Register               |     |

| 4.8.6   | DSPASURFLIVE—Primary A Live Surface Base Address          |     |

|         | nary B Plane Control                                      |     |

|         | DSPBCNTR—Primary B Control Register                       | 174 |

|         | DSPBLINOFF—Primary B Linear Offset Register               |     |

| 4.9.3   | DSPBSTRIDE—Primary B Stride Register                      |     |

| 4.9.4   | DSPBSURF—Primary B Surface Base Address Register          |     |

| 4.9.5   | DSPBTILEOFF—Primary B Tiled Offset Register               |     |

|         | DSPBSURFLIVE—Primary B Live Surface Base Address          |     |

|         | deo Sprite A Control                                      |     |

| 4.10.1  | DVSACNTR—Video Sprite A Control Register                  |     |

| 4.10.2  | DVSALINOFF—Video Sprite A Linear Offset Register          |     |

| 4.10.3  | DVSASTRIDE—Video Sprite A Stride Register                 |     |

| 4.10.4  | DVSAPOS—Video Sprite A Position Register                  |     |

| 4.10.5  | DVSASIZE—Video Sprite A Size Register                     |     |

| 4.10.6  | DVSAKEYVAL—Video Sprite A Color Key Value Register        |     |

| 4.10.7  | DVSAKEYMSK—Video Sprite A Color Key Mask Register         |     |

| 4.10.8  | DVSASURF—Video Sprite A Surface Address Register          |     |

| 4.10.9  | DVSAKEYMAXVAL—Video Sprite A Color Key Max Value Register |     |

| 4.10.10 |                                                           |     |

| 4.10.11 |                                                           |     |

| 4.10.12 |                                                           |     |

| 4.10.13 |                                                           |     |

|         | deo Sprite B Control                                      |     |

| 4.11.1  | DVSBCNTR—Video Sprite B Control Register                  |     |

| 4.11.2  | DVSBLINOFF—Video Sprite B Linear Offset Register          |     |

| 4.11.3  | DVSBSTRIDE—Video Sprite B Stride Register                 |     |

| 4.11.4  | DVSBPOS—Video Sprite B Position Register                  |     |

| 4.11.5  | DVSBSIZE—Video Sprite B Size Register                     |     |

| 4.11.6  | DVSBKEYVAL—Video Sprite B Color Key Value Register        |     |

| 4.11.7  | DVSBKEYMSK—Video Sprite B Color Key Mask Register         |     |

| 4.11.8  | DVSBSURF—Video Sprite B Surface Address Register          |     |

| 4.11.9  | DVSBKEYMAXVAL—Video Sprite B Color Key Max Value Register |     |

| 4.11.10 |                                                           |     |

| 4.11.11 |                                                           |     |

| 4.11.12 |                                                           |     |

| 4.11.13 | DVSBGAMC—Video Sprite B Gamma Correction Registers        | 214 |

|         |                                                           |     |

# 1. CPU Display Registers [DevSNB+]

This chapter discusses CPU Display Registers that are active in SandyBridge and later projects, unless indicated otherwise.

### 1.1 1.1 Introduction and Register Summary

This chapter contains the register descriptions for the display portion of a family of integrated graphics devices. These registers do vary by devices within the family of devices so special attention needs to be paid to which devices use which registers and register fields.

Different devices within the family may add, modify, or delete registers or register fields relative to another device in the same family based on the supported functions of that device.

The following table contains the sections break down where the register information is contained within this chapter:

| Address Range | Description            |

|---------------|------------------------|

| 40000h-4FFFFh | Shared Functions       |

| 60000h-6FFFFh | Pipe and Port Controls |

| 70000h-7FFFFh | Plane Controls         |

#### 1.1.1 Terminology

| Description                                    | Software Use                                                                                                                                                                           | Should be implemented as                                                                                                                                |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read/Write                                     | This bit can be read or written.                                                                                                                                                       |                                                                                                                                                         |

| Reserved                                       | Don't assume a value for these bits. Writes have no effect.                                                                                                                            | Writes are ignored. Reads return zero.                                                                                                                  |

| Reserved: write as zero,<br>must be zero, MBZ  | Software must always write a zero to these<br>bits. This allows new features to be added<br>using these bits that will be disabled when<br>using old software and as the default case. | Writes are ignored. Reads return<br>zero. Maybe be connected as<br>Read/Write in future projects.                                                       |

| Reserved: PBC, software must preserve contents | Software must write the original value back<br>to this bit. This allows new features to be<br>added using these bits.                                                                  | Read only or test mode<br>Read/Write.                                                                                                                   |

| Read Only                                      | This bit is read only. The read value is determined by hardware. Writes to this bit have no effect.                                                                                    | According to each specific bit. The bit value is determined by hardware and not affected by register writes to the actual bit.                          |

| Read/Clear                                     | This bit can be read. Writes to it with a one cause the bit to clear.                                                                                                                  | Hardware events cause the bit to<br>be set and the bit will be cleared on<br>a write operation where the<br>corresponding bit has a one for a<br>value. |

| Description     | Software Use                                                                                                                                                                                                                                                                                                                                                              | Should be implemented as                                                                                                                                                                                                                                                                                            |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Double Buffered | Write when desired. Read gives the<br>unbuffered value (written value) unless<br>specified otherwise. Written values will<br>update to take effect after a certain point.<br>Some have a specific arming sequence<br>where a write to another register is required<br>before the update can take place. This is<br>used to ensure atomic updates of several<br>registers. | Two stages of registers used. First<br>stage is written into and used for<br>readback (unless specified<br>otherwise). First stage value is<br>transferred into second stage at the<br>update point. Second stage value<br>is used to control hardware.<br>Arm/disarm flag needed for specific<br>arming sequences. |

#### 1.1.2 Display Mode Set Sequence

|    |                   | Wait values                                                                                           |

|----|-------------------|-------------------------------------------------------------------------------------------------------|

|    | CP                | U DP PLL warmup = 20uS                                                                                |

|    | CP                | U FDI transmitter PLL warmup = 10us                                                                   |

|    | DN                | l latency = 20uS                                                                                      |

|    | FD                | training pattern 1 time = 0.5uS                                                                       |

|    | FD                | training pattern 2 time = 1.5uS                                                                       |

|    | FD                | idle pattern time = 31uS                                                                              |

|    |                   | Enable sequence                                                                                       |

| 1. | Enable            | panel power as needed to retrieve panel configuration (use AUX VDD enable bit                         |

| 2. | Enable<br>enablin | PCH clock reference source and PCH SSC modulator, wait for warmup (Can be done anytime before g port) |

| 3. | lf enabl          | ing CPU embedded DisplayPort A: (Can be done anytime before enabling CPU pipe or port)                |

|    | a.                | Enable PCH 120MHz clock source output to CPU, wait for DMI latency                                    |

|    | b.                | Configure and enable CPU DisplayPort PLL in the DisplayPort A register, wait for warmup               |

| 4. | lf enabli         | ng port on PCH: (Must be done before enabling CPU pipe or FDI)                                        |

|    | a.                | Enable PCH FDI Receiver PLL, wait for warmup plus DMI latency                                         |

|    | b.                | Switch from Rawclk to PCDclk in FDI Receiver (FDI A OR FDI B)                                         |

|    | с.                | [DevSNB] Enable CPU FDI Transmitter PLL, wait for warmup                                              |

|    | d.                | [DevILK] CPU FDI PLL is always on and does not need to be enabled                                     |

| 5. | Enable            | CPU panel fitter if needed for hires, required for VGA (Can be done anytime before enabling CPU pipe) |

| 6. | Configu           | re CPU pipe timings, M/N/TU, and other pipe settings (Can be done anytime before enabling CPU pipe)   |

- 7. Enable CPU pipe

- 8. Configure and enable CPU planes (VGA or hires)

- 9. If enabling port on PCH:

- a. Program PCH FDI Receiver TU size same as Transmitter TU size for TU error checking

- b. Train FDI

- i. Set pre-emphasis and voltage (iterate if training steps fail)

- ii. Enable CPU FDI Transmitter and PCH FDI Receiver with Training Pattern 1 enabled.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | iii. Wait for FDI training pattern 1 time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | iv. Read PCH FDI Receiver ISR ([DevIBX-B+] IIR) for bit lock in bit 8 (retry at least once if no lock)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | v. Enable training pattern 2 on CPU FDI Transmitter and PCH FDI Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | vi. Wait for FDI training pattern 2 time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | vii. Read PCH FDI Receiver ISR ([DevIBX-B+] IIR) for symbol lock in bit 9 (retry at least once if no lock)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | viii. Enable normal pixel output on CPU FDI Transmitter and PCH FDI Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ix. Wait for FDI idle pattern time for link to become active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| С.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Configure and enable PCH DPLL, wait for PCH DPLL warmup (Can be done anytime before enabling PCH transcoder)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| d.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | [DevCPT] Configure DPLL SEL to set the DPLL to transcoder mapping and enable DPLL to the transcoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| e.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | [DevCPT] Configure DPLL_CTL DPLL_HDMI_multipler.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| f.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Configure PCH transcoder timings, M/N/TU, and other transcoder settings (should match CPU settings).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| g.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | [DevCPT] Configure and enable Transcoder DisplayPort Control if DisplayPort will be used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| h.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Enable PCH transcoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10. Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ports (DisplayPort must enable in training pattern 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11. Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | panel power through panel power sequencing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12. Wait for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | r panel power sequencing to reach enabled steady state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13. Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | panel power override                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14. If Displa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ayPort, complete link training                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15 Enchi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| is. Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | panel backlight                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ID. ENADIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | panel backlight Disable sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1. Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Disable sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ol> <li>Disable</li> <li>Disable</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Disable sequence<br>Panel backlight                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <ol> <li>Disable</li> <li>Disable</li> <li>Disable</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Disable sequence           Panel backlight           panel power through panel power sequencing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <ol> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Disable sequence         Panel backlight         panel power through panel power sequencing         CPU planes (VGA or hires)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <ol> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>[DevlLk</li> <li>Disable</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Disable sequence         Panel backlight         panel power through panel power sequencing         CPU planes (VGA or hires)         K-A] Disable CPU panel fitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <ol> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>[DevlLk</li> <li>Disable</li> <li>Wait for</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Disable sequence<br>Panel backlight<br>panel power through panel power sequencing<br>CPU planes (VGA or hires)<br>(-A] Disable CPU panel fitter<br>CPU pipe                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <ol> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>[DevILk</li> <li>Disable</li> <li>Wait for</li> <li>If disable</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Disable sequence         Panel backlight         panel power through panel power sequencing         CPU planes (VGA or hires)         K-A] Disable CPU panel fitter         CPU pipe         r CPU pipe off status (CPU pipe config register pipe state)                                                                                                                                                                                                                                                                                                                                                                              |

| <ol> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>[DevILk</li> <li>Disable</li> <li>Wait for</li> <li>If disable</li> <li>Disable</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                     | Disable sequence<br>Panel backlight<br>panel power through panel power sequencing<br>CPU planes (VGA or hires)<br>K-A] Disable CPU panel fitter<br>CPU pipe<br>r CPU pipe<br>r CPU pipe off status (CPU pipe config register pipe state)<br>ling DisplayPort on PCH, write the DisplayPort control register bit 31 to 0b.                                                                                                                                                                                                                                                                                                             |

| <ol> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>[DevILk</li> <li>Disable</li> <li>Wait for</li> <li>If disable</li> <li>Disable</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                     | Disable sequence         Panel backlight         panel power through panel power sequencing         CPU planes (VGA or hires)         K-A] Disable CPU panel fitter         CPU pipe         r CPU pipe off status (CPU pipe config register pipe state)         ling DisplayPort on PCH, write the DisplayPort control register bit 31 to 0b.         CPU panel fitter (Can be done anytime after CPU pipe is off)                                                                                                                                                                                                                   |

| <ol> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>[DevILk</li> <li>Disable</li> <li>Wait for</li> <li>If disable</li> <li>Disable</li> <li>Disable</li> <li>If disable</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                 | Disable sequence         Panel backlight         panel power through panel power sequencing         CPU planes (VGA or hires)         K-A] Disable CPU panel fitter         CPU pipe         r CPU pipe off status (CPU pipe config register pipe state)         ling DisplayPort on PCH, write the DisplayPort control register bit 31 to 0b.         CPU panel fitter (Can be done anytime after CPU pipe is off)         ling CPU embedded DisplayPort A                                                                                                                                                                           |

| <ol> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>[DevILk</li> <li>Disable</li> <li>Wait for</li> <li>If disable</li> <li>Disable</li> <li>If disable</li> <li>If disable</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                              | Disable sequence         Panel backlight         panel power through panel power sequencing         CPU planes (VGA or hires)         K-A] Disable CPU panel fitter         CPU pipe         r CPU pipe off status (CPU pipe config register pipe state)         ling DisplayPort on PCH, write the DisplayPort control register bit 31 to 0b.         CPU panel fitter (Can be done anytime after CPU pipe is off)         ling CPU embedded DisplayPort A         Disable port                                                                                                                                                      |

| <ol> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>[DevILk</li> <li>Disable</li> <li>Wait for</li> <li>If disable</li> <li>Disable</li> <li>If disable</li> <li>If disable</li> <li>a.</li> <li>c.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                      | Disable sequence         Panel backlight         panel power through panel power sequencing         CPU planes (VGA or hires)         K-A] Disable CPU panel fitter         CPU pipe         r CPU pipe off status (CPU pipe config register pipe state)         ling DisplayPort on PCH, write the DisplayPort control register bit 31 to 0b.         CPU panel fitter (Can be done anytime after CPU pipe is off)         ling CPU embedded DisplayPort A         Disable port         Disable CPU DisplayPort PLL in the DisplayPort A register                                                                                    |

| <ol> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>[DevILk</li> <li>Disable</li> <li>Wait for</li> <li>If disable</li> <li>Disable</li> <li>If disable</li> <li>If disable</li> <li>a.</li> <li>c.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                      | Disable sequence         Panel backlight         panel power through panel power sequencing         CPU planes (VGA or hires)         K-A] Disable CPU panel fitter         CPU pipe         r CPU pipe off status (CPU pipe config register pipe state)         ling DisplayPort on PCH, write the DisplayPort control register bit 31 to 0b.         CPU panel fitter (Can be done anytime after CPU pipe is off)         ling CPU embedded DisplayPort A         Disable port         Disable CPU DisplayPort PLL in the DisplayPort A register         Disable PCH 120MHz clock source output to CPU                              |

| <ol> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Disable</li> <li>Wait for</li> <li>If disable</li> <li>Disable</li> <li>If disable</li> </ol> | Disable sequence         Panel backlight         panel power through panel power sequencing         CPU planes (VGA or hires)         K-A] Disable CPU panel fitter         CPU pipe         r CPU pipe off status (CPU pipe config register pipe state)         ling DisplayPort on PCH, write the DisplayPort control register bit 31 to 0b.         CPU panel fitter (Can be done anytime after CPU pipe is off)         ling CPU embedded DisplayPort A         Disable port         Disable CPU DisplayPort PLL in the DisplayPort A register         Disable PCH 120MHz clock source output to CPU         sabling port on PCH: |

- d. Wait for PCH transcoder off status (PCH transcoder config register transcoder state)

- e. [DevCPT] Disable Transcoder DisplayPort Control if DisplayPort was used

- f. [DevCPT] Disable Transcoder DPLL Enable bit in DPLL\_SEL

- g. Disable PCH DPLL (Can be done anytime after PCH ports and transcoder are off)

- h. If no other PCH transcoder is enabled

- i. Switch from PCDclk to Rawclk in PCH FDI Receiver