### Intel<sup>®</sup> Iris<sup>®</sup> X<sup>e</sup> MAX Graphics Open Source

### **Programmer's Reference Manual**

### For the 2020 Discrete GPU formerly named "DG1"

Volume 6: Memory Views

February 2021, Revision 1.0

### **Notices and Disclaimers**

Intel technologies may require enabled hardware, software or service activation.

No product or component can be absolutely secure.

Code names are used by Intel to identify products, technologies, or services that are in development and not publicly available. These are not "commercial" names and not intended to function as trademarks.

Customer is responsible for safety of the overall system, including compliance with applicable safetyrelated requirements or standards.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

### **Table of Contents**

| Memory Views                            | 1  |

|-----------------------------------------|----|

| Introduction                            | 1  |

| Memory Views Glossary                   | 3  |

| Graphics Virtual Memory                 | 3  |

| Graphics Translation Tables             | 3  |

| Virtual Addressed TR Translation Tables | 10 |

| Walk with 64KB Page                     |    |

| PDE for Page Table                      | 19 |

| PTE: Page Table Entry for 64KB Page     | 20 |

| PTE: Page Table Entry for 4KB Page      | 21 |

| Walk with 64KB Page                     | 23 |

| Walk with 2MB Page                      | 24 |

| Pointer to PML4 table                   | 26 |

| PML4E: Pointer to PDP Table             | 26 |

| PDPE: Pointer to PD Table               | 26 |

| PDPE for PD                             | 27 |

| PDPE for 1GB Page                       | 28 |

| PD: Pointer to Page Table               | 29 |

| PDE for Page Table                      | 29 |

| PDE for 2MB Page                        |    |

| PTE: Page Table Entry for 64KB Page     |    |

| PTE: Page Table Entry for 4KB Page      |    |

### **Memory Views**

### Introduction

The hardware supports three engines:

- The Render command streamer interfaces to 3D/IE and display streams.

- The Media command streamer interfaces to the fixed function media.

- The Blitter command streamer interfaces to the blit commands.

Software interfaces of all three engines are very similar and should only differ on engine-specific functionality.

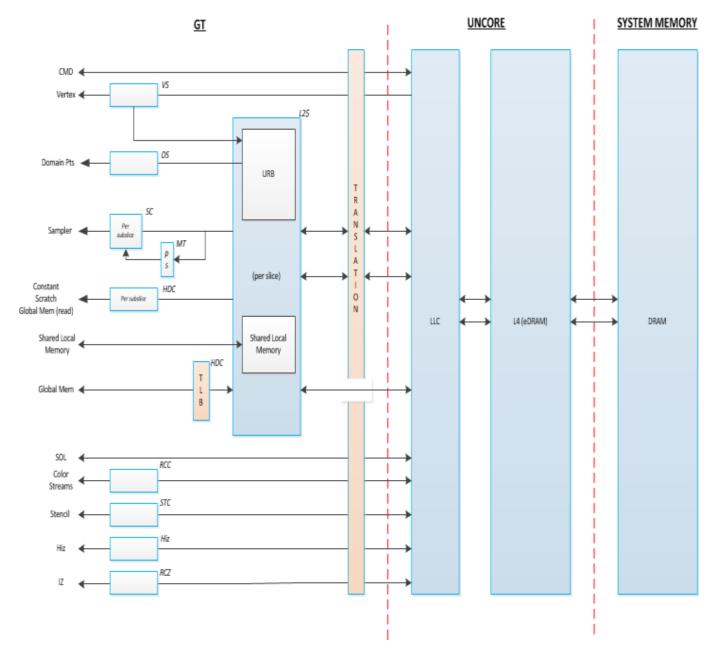

#### **Cache and Memory Hierarchy**

#### **Memory Views Glossary**

| Term                 | Definition                                                                                                  |

|----------------------|-------------------------------------------------------------------------------------------------------------|

| IOMMU                | I/O Memory Mapping unit                                                                                     |

| SVM                  | Shared Virtual Memory, implies the same virtual memory view between the IA cores and processor graphics.    |

| Page Walker<br>(GAM) | GFX page walker which handles page level translations between GFX virtual memory to physical memory domain. |

#### **Graphics Virtual Memory**

The GPU uses a virtual memory address space, where the graphics virtual address is mapped through a Page Table (PPGTT) to a physical memory address. Normally, this mapping is set up by the graphics device driver and is private to the GPU context. However, in some cases the graphics virtual address is shared with the CPU - see for more information.

The range of valid graphics virtual addresses, and the types of page tables supported for address translation, varies with the GPU configuration. See the section for a summary the ranges and features supported by a specific graphics device.

Although the range of supported graphics virtual addresses varies, most GPU commands and GPU instructions use a common 64-bit definition for a graphics virtual address. Addresses outside of the supported range are reserved for future address space expansion. See the **GraphicsAddress** structure definition for specific details.

Some GPU devices support an extended graphics virtual memory address mapping called Tiled Resources. When enabled, the Tiled Resources Translation Table (TR-TT) pre-processes graphics virtual addresses. TR-TT maps a graphics virtual memory address either to a new graphics virtual memory address or to a Null Tile. Null Tiles return zero on reads and drop writes. For translations that are not Null Tiles, the new graphics virtual memory address is then used for the graphics virtual address and translated through the normal Page Table to generate a physical memory address.

#### **Graphics Translation Tables**

GT supports standard virtual memory models as defined by the IA programmer's guide. This section describes the different paging models, their behaviors, and the page table formats.

The Graphics Translation Tables GTT (Graphics Translation Table, sometimes known as the global GTT) and PPGTT (Per-Process Graphics Translation Table) are memory-resident page tables containing an array of DWord Page Translation Entries (PTEs) used in mapping logical Graphics Memory addresses to physical memory addresses, and sometimes snooped system memory "PCI" addresses.

The base address (MM offset) of the GTT and the PPGTT are programmed via the PGTBL\_CTL and PGTBL\_CTL2 MI registers, respectively. The translation table base addresses must be 4KB aligned. The GTT size can be either 128KB, 256KB, or 512KB (mapping to 128MB, 256MB, and 512MB aperture sizes respectively) and is physically contiguous. The global GTT should only be programmed via the range defined by GTTMMADR. The PPGTT is programmed directly in memory. The per-process GTT (PPGTT) size is controlled by the PGTBL\_CTL2 register. The PPGTT can, in addition to the above sizes, also be 64KB

in size (corresponding to a 64MB aperture). Refer to the GTT Range chapter for a bit definition of the PTE entries.

#### **GFX Page Tables**

GPU supports three-page table mechanisms

- IA32e compatible GTT

- PPGTT private per process GTT (private GFX)

- GGTT global GTT

All page tables use the same 64-bit PTE format. Differences are in how various bit fields applies (vs reserved) under various usage models.

Follows the same principles that were set it up for improved page tables and compatibility of OS managed page table formats.

#### **Tiled Resources Translation Tables**

Sparse Tiled Resources can be thought of as a kind of application-controlled virtual memory scheme. The application allocates a resource in a virtual address space. Then the application tells the driver to map specified 64KB tiles within the surface to memory, within resources called Tile Pools. Tiles that are not mapped to a Tile Pool are null tiles.

Tiled Resource Translation Table (TRTT) is constructed as a 3-level tile Table. Each tile is 64KB in size which leaves behind 44-16=28 address bits. 28bits are partitioned as 9+9+10 which corresponds to TRVATT L3, L2 and L1 respectively. This is where TRVATT L3 has 512 entries, L2 has 512 entries and L1 has 1024 entries where each level is contained within a 4KB page hence L3 and L2 is composed of 64b entries and L1 is composed of 32b entries.

| 6 6 6<br>3 2 1 | 4 4 4<br>9 8 7 | 6 | 3 3 3 3 2 2<br>3 2 1 0 9 8 |        | 1 1 1 1 1 1 1 1<br>8 7 6 5 4 3 2 | 1 1 9 8 7 6 5 4 3<br>1 0 | 2 1 0             |                    |

|----------------|----------------|---|----------------------------|--------|----------------------------------|--------------------------|-------------------|--------------------|

| Ignored        |                |   | Address of the TRVA        | ATT-L2 |                                  | Ignored                  | N I<br>un<br>II v | TRVATT-L3<br>entry |

| Ignored | Address of the TRVATT-L1 | Ignored | N I<br>u n<br>II v<br>II v |

|---------|--------------------------|---------|----------------------------|

|---------|--------------------------|---------|----------------------------|

| Tile Virtual Address TRVATT-L1 entry | Tile Virtual Address | TRVATT-L1<br>entry |

|--------------------------------------|----------------------|--------------------|

|--------------------------------------|----------------------|--------------------|

The contents of the TRVATT tables are as listed above where L3 and L2 points to the address of the next level which is a 4KB page and L1 contains the 32b VA address pointer needed to map the TR tile to virtual address space.

#### L1 Entry:

| Bits | Field         | Description                                                                           |  |

|------|---------------|---------------------------------------------------------------------------------------|--|

| 31:0 | ADDR: Address | GFX virtual address of 64KB tile is referenced by this entry.                         |  |

|      |               | This field is treated as GFX Virtual Address (GVA) when translated and maps to 47:16. |  |

#### L2 Entry:

| Bits  | Field            | Description                                                                                                                                                                                                               |

|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63:48 | Ignored          | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                         |

| 47:12 | ADDR:<br>Address | GFX virtual address or Guest Physical Address of 4KB base address pointing to TR-TT L1.<br>TR-TT table entries for L2 and L3 can be in GFX virtual address mode or Guest Physical address<br>mode chosen by GFX software. |

| 11:2  | Ignored          | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                         |

| 1     | Null             | Null Tile where reads to this tile returns zero with a Null indicator and writes are dropped.                                                                                                                             |

| 0     | Invalid          | Invalid Tile where reads to this tile returns zero and writes are dropped. Additional interrupt is generated to GFX software when an invalid tile is accessed.                                                            |

#### L3 Entry:

| Bits  | Field            | Description                                                                                                                                                                                                               |

|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63:48 | Ignored          | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                         |

| 47:12 | ADDR:<br>Address | GFX virtual address or Guest Physical Address of 4KB base address pointing to TR-TT L2.<br>TR-TT table entries for L2 and L3 can be in GFX virtual address mode or Guest Physical address<br>mode chosen by GFX software. |

| 11:2  | Ignored          | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                         |

| 1     | Null             | Null Tile where reads to this tile returns zero with a Null indicator and writes are dropped.                                                                                                                             |

| 0     | Invalid          | Invalid Tile where reads to this tile returns zero and writes are dropped. Additional interrupt is generated to GFX software when an invalid tile is accessed.                                                            |

| Programming Note                                                                                                                                                         |                                                     |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|

| Context:                                                                                                                                                                 | Tiled ResourceTranslation Tables in Gfx Page Tables |  |

| GFX Driver has to disable the TR-TT bypass mode before using tiled resources translation tables. Details of the registers are given in "registers for TR-TT management." |                                                     |  |

|                                                                                                                                                                          |                                                     |  |

|                                                                  | Programming Note                                    |

|------------------------------------------------------------------|-----------------------------------------------------|

| Context:                                                         | Tiled ResourceTranslation Tables in Gfx Page Tables |

| GFX Driver is not allowed to put TR-TT entries into TR-VA space. |                                                     |

| Programming Note                                                                       |                                                     |  |

|----------------------------------------------------------------------------------------|-----------------------------------------------------|--|

| Context:                                                                               | Tiled ResourceTranslation Tables in Gfx Page Tables |  |

| Usage model for TR translations are restricted to GFX Render Engine (& POSH pipeline). |                                                     |  |

| Programming Note                                             |                                                                                                                                                      |  |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Context: Tiled ResourceTranslation Tables in Gfx Page Tables |                                                                                                                                                      |  |

|                                                              | TRTT is only for PPGTT64 (Advanced or Legacy PPGTT64). Enabling TRTT in Legacy PPGTT32 context or GGTT context is considered as invalid programming. |  |

| Programming Note                                                                                              |                                                              |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|

| Context:                                                                                                      | Context: Tiled ResourceTranslation Tables in Gfx Page Tables |  |  |  |  |

| When partitioned address space based Dual Context is enabled, bit[47] of the virtual address in L3, L2 and L1 |                                                              |  |  |  |  |

| entries must be 0.                                                                                            | entries must be 0.                                           |  |  |  |  |

#### **Registers for TR-TT Management**

Following register is a global mechanism to disable the bypass mode which is considered to be default for h/w. GFX driver has to set this bit to disable bypass mode before using TR-TTs.

Following registers shall be part of the h/w context.

|                                     |                      | Tiled Resources VA Translation                                                                                                         | n Table L3 Pointer    |           |  |  |

|-------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------|--|--|

| Register Space:         MMIO: 0/2/0 |                      |                                                                                                                                        |                       |           |  |  |

| DWord                               | Bit                  | Description                                                                                                                            |                       |           |  |  |

| 1                                   | 63:48                | Reserved                                                                                                                               |                       |           |  |  |

|                                     |                      | Access: RO                                                                                                                             |                       |           |  |  |

|                                     |                      | Reserved.                                                                                                                              |                       |           |  |  |

|                                     | 47:32                | Tiled Resource - VA translation Table L3 Pointer (Upper Address)                                                                       |                       |           |  |  |

|                                     | Default Value: 0000h |                                                                                                                                        |                       |           |  |  |

|                                     |                      | Access:                                                                                                                                |                       | R/W       |  |  |

|                                     |                      | Upper address bits for tiled resource VA to virtual address translation L3 table.                                                      |                       |           |  |  |

|                                     |                      | For physical memory option, address bits [47:39] has to be programmed to "0" as it is defined the limit of physical memory allocation. |                       |           |  |  |

| 0                                   | 31:16                | Tiled Resource - VA translation Table L3 Pointer (Lower Address)                                                                       |                       |           |  |  |

|                                     |                      | Default Value:                                                                                                                         |                       | 0000h     |  |  |

|                                     |                      | Access:                                                                                                                                |                       | R/W       |  |  |

|                                     |                      | Lower address bits for tiled resource VA to virtua                                                                                     | l address translatior | L3 table. |  |  |

| Tiled Resources VA Translation Table L3 Pointer |           |    |  |  |

|-------------------------------------------------|-----------|----|--|--|

| <sup>15:0</sup> Reserved                        |           |    |  |  |

|                                                 | Access:   | RO |  |  |

|                                                 | Reserved. |    |  |  |

|                                                                                                                                                                                         | Tiled Resources Null Tile Detection Register |         |          |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------|----------|--|--|--|

| Registe                                                                                                                                                                                 | Register Space:     MMIO: 0/2/0              |         |          |  |  |  |

| DWord Bit Description                                                                                                                                                                   |                                              |         |          |  |  |  |

| <sup>31:0</sup> Null Tile Detection Value                                                                                                                                               |                                              |         |          |  |  |  |

|                                                                                                                                                                                         | Default Value:                               |         | 0000000h |  |  |  |

| Access:                                                                                                                                                                                 |                                              | Access: | R/W      |  |  |  |

| A 32bit value programmed to enable h/w to perform a match of TR-VA TT entries to detect N<br>Tiles. Hardware will flag each entry and space behind it as Null Tile for matched entries. |                                              |         |          |  |  |  |

|                             | Tiled Resources Invalid Tile Detection Register                                                                                                                                                  |     |         |          |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|----------|--|

| Register Space: MMIO: 0/2/0 |                                                                                                                                                                                                  |     |         |          |  |

| DWord Bit Description       |                                                                                                                                                                                                  |     | ription |          |  |

|                             | <sup>31:0</sup> Invalid Tile Detection Value                                                                                                                                                     |     |         |          |  |

|                             | Default Value:                                                                                                                                                                                   |     |         | 0000000h |  |

| Access: R/W                 |                                                                                                                                                                                                  | R/W |         |          |  |

|                             | A 32bit value programmed to enable h/w to perform a match of TR-VA TT entries to detect Invalid<br>Tiles. Hardware will flag each entry and space behind it as Invalid Tile for matched entries. |     |         |          |  |

|         | Tiled Resources Virtual Address Detection Registers (TRVADR) |                |  |       |  |  |

|---------|--------------------------------------------------------------|----------------|--|-------|--|--|

| Registe | Register Space: MMIO: 0/2/0                                  |                |  |       |  |  |

| DWord   | DWord Bit Description                                        |                |  |       |  |  |

| 0       | 31:8                                                         | Reserved       |  |       |  |  |

|         |                                                              | Access:        |  | RO    |  |  |

|         |                                                              | Reserved.      |  |       |  |  |

|         | 7:4 TRVA Mask Value (TRVAMV)                                 |                |  |       |  |  |

|         |                                                              | Default Value: |  | 0000b |  |  |

|         |                                                              | Access:        |  | R/W   |  |  |

#### **Tiled Resources Virtual Address Detection Registers (TRVADR)**

4bit MASK value that is mapped to incoming address bits[47:44]. MASK bits are used to identify which address bits need to be considered for compare. If particular mask bit is "1", mapping address bit needs to be compared to DATA value provided. If "0", corresponding address bit is masked which makes it don't care for compare (*this field defaults to "0000" to disable detection*)

Note that h/w supports two possible values for MASK: "0000" which is disabled case and "1111" where 44 bit TR-VA space is carved out.

# 3:0 TRVA Data Value (TRVADV) Default Value: 0b Access: R/W

4bit DATA value that is mapped to incoming address bits[47:44]. Data bits are used to compare address values that are not filtered by the TRVAMV for match.

|         | Tiled Resources Translation Table Control Register (TRTTE)                                                                                        |                                                                                                                                    |                            |                     |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------|--|--|--|

| Registe | Register Space: MMIO: 0/2/0                                                                                                                       |                                                                                                                                    |                            |                     |  |  |  |

| DWord   | Bit                                                                                                                                               | Des                                                                                                                                | cription                   |                     |  |  |  |

| 0       | 31:2                                                                                                                                              | Reserved                                                                                                                           |                            |                     |  |  |  |

|         |                                                                                                                                                   | Access:                                                                                                                            | RO                         |                     |  |  |  |

|         |                                                                                                                                                   | Reserved.                                                                                                                          |                            |                     |  |  |  |

|         | 1                                                                                                                                                 | TR-VA Translation Table Memory Location                                                                                            |                            |                     |  |  |  |

|         |                                                                                                                                                   | Default Value:                                                                                                                     |                            | 0b                  |  |  |  |

|         |                                                                                                                                                   | R/W                                                                                                                                |                            |                     |  |  |  |

|         |                                                                                                                                                   | This fields specifies whether the translation tables for TR-VA to VA are in virtual address space vs physical (GPA) address space. |                            |                     |  |  |  |

|         |                                                                                                                                                   | 0: Tables are in Physical (GPA) Space                                                                                              |                            |                     |  |  |  |

|         |                                                                                                                                                   | 1: Tables are in Virtual Address Space                                                                                             |                            |                     |  |  |  |

|         | Tiled Resource Translation Tables in GPA space is not supported in any generations. This r<br>should never be set as GPA mode (always set to '1). |                                                                                                                                    |                            |                     |  |  |  |

|         | 0                                                                                                                                                 | TR-TT Enable                                                                                                                       |                            |                     |  |  |  |

|         |                                                                                                                                                   | Default Value:                                                                                                                     |                            | 0b                  |  |  |  |

|         |                                                                                                                                                   | Access:                                                                                                                            |                            | R/W                 |  |  |  |

|         |                                                                                                                                                   | TR translation tables are disabled as default. This translation active.                                                            | s field needs to be enable | d via s/w to get TR |  |  |  |

The following register (0x4DFC[0]) has enable and disable control of the bypass path across TR translations. By default, bypass is enabled, and bypass needs to be disabled (by setting 0x4DFC[0] = '1) for TR translations to function. Disabling the bypass should be done before render power gating is enabled.

#### **Detection and Treatment of Null and Invalid Tiles**

Two types of definition that need to be extracted from TR-VA walk in addition to reaching the GFX virtual address.

- 1. **Null Tiles**: Null tiles provide the applications the of capability to preventing OS mapping the entire surface. When a memory access hits a Null tile, the access is terminated and zero's are returned to the originator of the memory access for loads along with a null indicator and for stores the access is dropped at the page walker level.

- 2. **Invalid Tiles**: This is the case where GFX software did not update the value of the mapping properly for hardware to separate resident vs null tiles. The Invalid Tile treatment is exactly same however additionally a unique interrupt is generated in h/w

Both detections are done by GPU:

- For L2/L3 entries, Null and Invalid tile information is already embedded in the TR-TT entries

- For L1 entries, the contents (32bits) are compared in hardware to pre-programmed values by GFX software (*values are provided in GFX MMIO space*). For the match values, two separate 32b registers are defined, one for Null Tile detection and one for Invalid Tile detection.

Hardware walking matching the value or detecting L2/L3 would terminate the walk (i.e. rest of the tables are not valid) and define the access as either Null or Invalid.

| Programming Note |                                                                       |  |  |  |

|------------------|-----------------------------------------------------------------------|--|--|--|

| Context:         | Detection and treatment of null and invalid tiles.                    |  |  |  |

| The software i   | s not allowed to program both Null and Invalid values to be the same. |  |  |  |

| Programming Note                                           |                               |  |  |  |

|------------------------------------------------------------|-------------------------------|--|--|--|

| Context:                                                   | TileX Surfaces and Null Tiles |  |  |  |

| NULL or Invalid Tiles are not supported on TileX surfaces. |                               |  |  |  |

GPU implements a counter mechanism to roll-up the Null tile accesses detected. The counter value is exposed to GFX software via GFX MMIO.

Implementation, when the TR translation tables are in Gfx virtual address domain, the pages faults encountered while walking the IA32e pages are not reported back to the TR walkers or TLBs. These faults are handled as fault & halt, making these faults transparent to the TR walkers. However, when such a fault is not fixed (unsuccessful fault response) or when a non-recoverable fault encountered, main page walker HW converts the cycle to an invalid cycle. Thus, in this case, TR walker or TR TLBs will get incorrect read return data without any notification of the non-recoverable fault condition. Thus, TR walker/TLBs will

continue with the TR-walk with incorrect data. This can lead to spurious cycles being generated. However, a *Gfx reset/FLR is expected as a result of the non-recoverable fault.*

#### **TR-TT Modes**

The L3 table pointer along with TRTTL3e/TRTTL2e is projected to support two modes of address space. Original intent was to have the contents to be in Virtual Address space (OS managed) and have them to be translated to GPA to HPA before getting accessed. Such mechanism will incur high latency penalties due to nested page translations. GPU shall have an additional mode where tiled-resources translation tables are in physical address space (GPA) and eliminate the need to have nested translations to reduce the potentially high miss latencies.

TR-TT walker shall have both modes supported. The Mode bit will be part of the same Register that provides TR-VA TT L3 pointer.

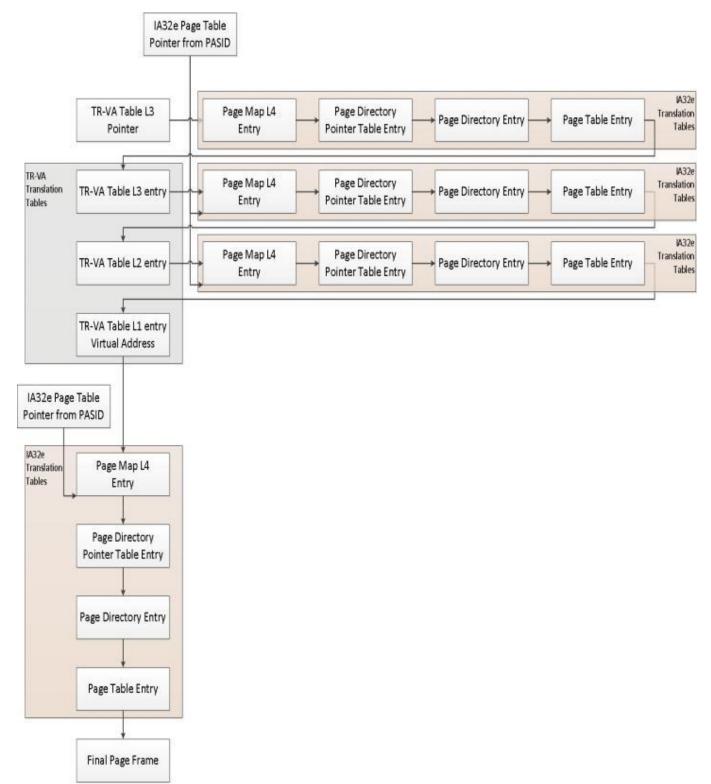

### **Virtual Addressed TR Translation Tables**

Having sparse tiled resource translation tables in GFX virtual space requires the h/w TR-TT walker to walk thru the 1<sup>st</sup> level tile tables for table accesses to reach to Physical address at the L1 TR translation tables.

The following diagrams provide the view of the walk TR-VA translation tables are in physical memory and no 2<sup>nd</sup> Level (VTd) translations enabled.

Once 2<sup>nd</sup> level translations are enabled each level of 1<sup>st</sup> level walk needs to be further walked through VTd page tables.

The level of nested walks does not change the structure of the TR-VA walker; it just defines the recursive nature of the translations.

#### TR-TT Page Walk

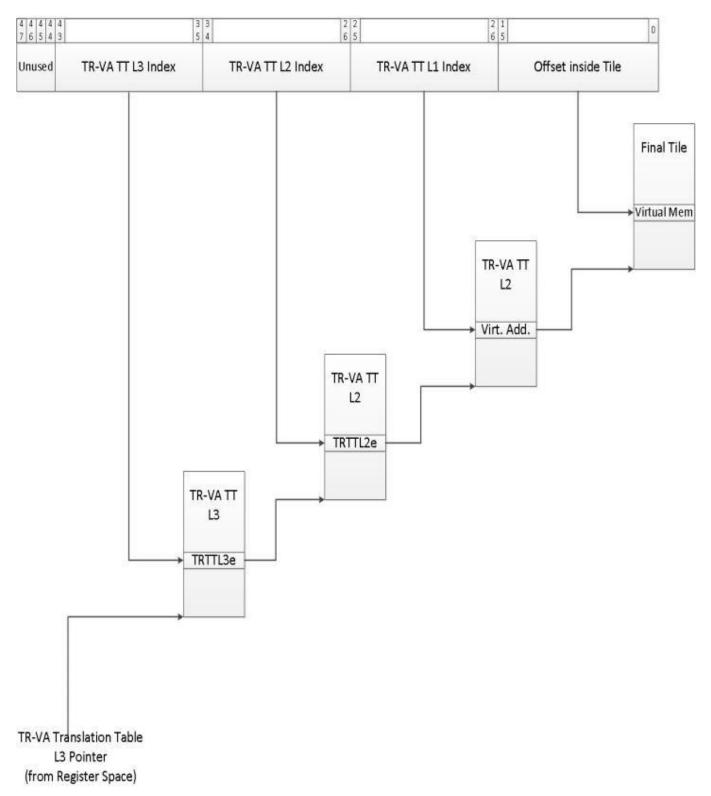

Sparse Tiled Resources translation tables are separated into 3-levels. The pointer to L3 table is going to be set up in GFX MMIO space as part of the context, this pointer be would be available to page walker ahead of any TR-VA memory accesses.

TR-TT L3 walk will be consistent of calculating the 64b of interest based on the L3 table pointer and using the 9 bit index (address bits[43:35]). L2 will use TR-TT L3 entry as the table pointer and use the next set of 9 address bits ([34:26]) to locate the L2 entry which is a pointer to L1 table. Final L1 table is located with L2 entry and indexed by remaining 10 address bits (25:16) to index where 32b virtual address is extracted.

Post TR-TT walk 32b entry from L1 is mapped to final virtual address 47:16 and remaining 15:0 is passed from the original TR-VA access as is given all tiles in TR-VA space are 64KB in size.

#### Page Table Modes

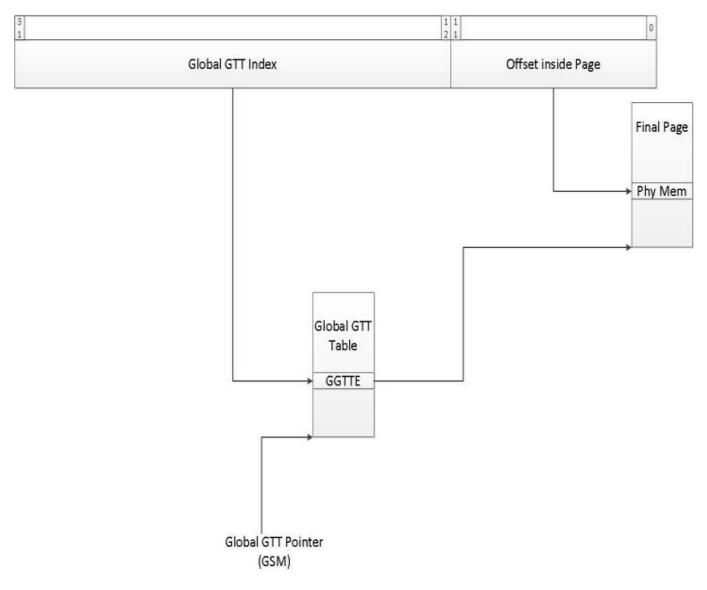

GFX Aperture and Display accesses are mapped thru Global GTT to keep the walk simple (i.e. 1-level) and latency sensitive. GPU accesses to memory can be mapped via Global GTT and/or ppGTT with various addressing modes.

Supported walk modes are listed as following:

- 1. **Global GTT with 32b virtual addressing**: Global GTT usage is similar to previous generations with extended capability of increasing virtual address (VA) up to 4GB (from 2GB) and use a standard 64b PTE format. The breakdown of the PTE for global GTT is given in later sections and allows 1-level page walk where the 20b index is used to select the 64b PTE from memory.

- 2. **Legacy 32b VA with ppGTT**: This is a mode where ppGTT page tables are considered private and managed via GFX sotfware (driver) where context is tagged as Legacy 32b VA. Each page walk is managed via 9b of the virtual address and 20b index to address 4GB memory space is broken into 3 parts. In order to optimize the walks and make it look like previous generations, GFX sotfware provides 4 pointers to page tables (called 4 PDP entries) all guest physical address. GPU uses the four pointers and fetches the 4x4KB into h/w (for render and media) before the context execution starts. The optimization limits the dynamic (on demand) page walks to 1-level only.

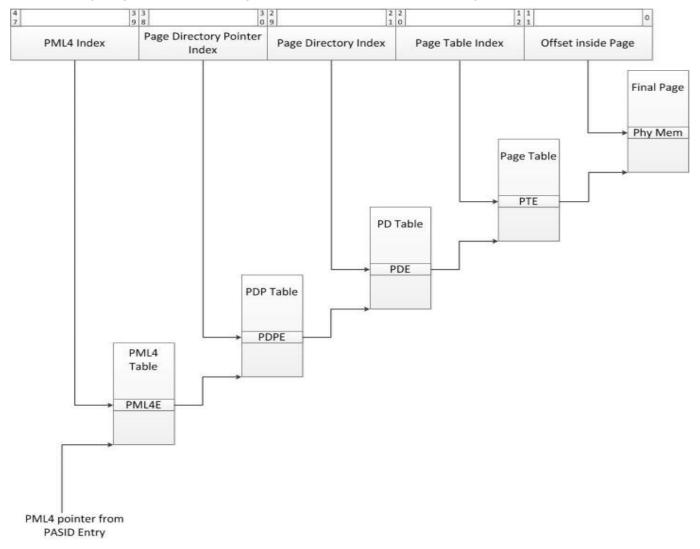

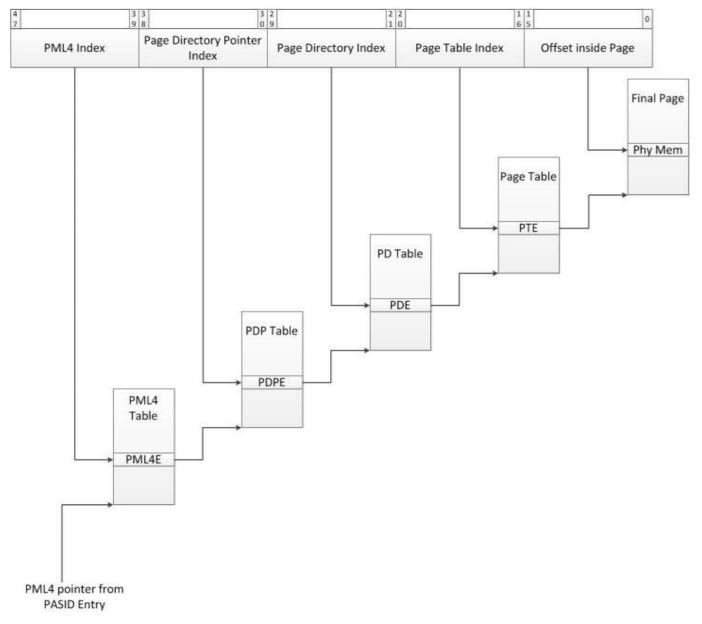

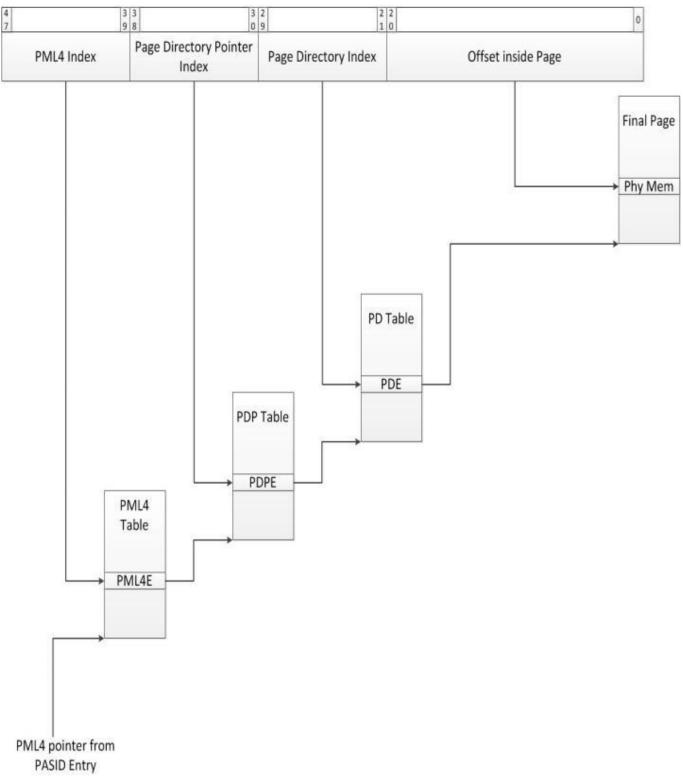

- 3. **Legacy 48b VA with ppGTT**: GFX address expansion beyond 4GB is added to address 48b virtual address space. 48b VA requires 36b indexing (4x9b) translating into 4-levels of page walk. To reduce the overhead of 4 level walk, GPU will cache the entire content of PML4 (4kB) to limit the on-demand walks to 3 levels. The caching happens as part of the initial demand where no further replacements required.

- 4. Advanced 48b VA with IA32e support via IOMMU: 48b addressing in advanced mode is managed via IOMMU settings where the base of the page table shall be found after the root / context tables using bus/device/function values. PASID# is used as an index in PASID table to find page table pointer to start the 4-level page walk. Rest of the mechanism is similar to Legacy 48b VA mode, GPU has the capability to cache entire content of PML4 and try to limit the dynamic page walks to 3-level.

#### **Global GTT**

The Global GTT mechanism looks very similar to previous with the distinction of page table entry. Aperture and display will still use the global GTT even if GT core is mapped via per-process GTT.

The PTE format is updated to match per process GTT definitions and GSM is now expanded in size (2MB=>8MB) to cover for the entire 4GB (32b virtual addressing) space. Each entry corresponding to a 4KB page with 2^20 entries in GSM (each with 8B content)

For "*MI\_update\_GTT*", the page address provided 31:12 need to be shifted down to 22:3 for the correct QW position within the GGTT.

#### Page Table Entry

The following page table entry will be used for Global GTT:

| 6 6 6 6 5 5 5<br>3 2 1 0 9 8 7 |                        | HAW HAW                                                                                                                                      | 3         3         2         2         2         2         2         2         2         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |                     |

|--------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------|

| Ignored                        |                        |                                                                                                                                              | Address to Final Page (4KB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Ignored P                                            | Global GTT<br>Entry |

| Bits                           | Bits Field Description |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |                     |

| 63:57                          | Ignored                | Ignored                                                                                                                                      | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                      |                     |

| 51:HAW                         | Ignored                | Ignored                                                                                                                                      | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                      |                     |

| (HAW-1):12                     | Address                | Physical address of 4KB memory page referenced by this entry.                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |                     |

| 11:5                           | Ignored                | Ignored (h/w does not care about values behind ignored registers)                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |                     |

| 4:2                            | Function<br>Number     | The Number of the Function to which this page has been assigned. This field is ignored unless HW Graphics Virtualization (SRIOV) is enabled. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |                     |

| 1                              | Ignored                | Ignored (h/w does not care about values behind ignored registers)                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |                     |

| 0                              | Present                | When set to 1, indicates that this Page Table Entry is Valid, and the corresponding page is Present in physical memory                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |                     |

\* HAW = 39 for client, and 46 for server.

The GPU accesses GGTT table entries as uncacheable.

#### Page Walk

The global GTT page walk is identical to what it was before. The only difference would be that each entry is 8B (instead of 4B) hence the entry selection needs to be updated once the corresponding Page Table miss read is returned.

#### Per-Process GTT with 32b VA

Page walker is capable supporting 32b VA address with optimized page tables, this is to keep the walk to a single level.

#### Page Walk in Legacy mode with 32b VA

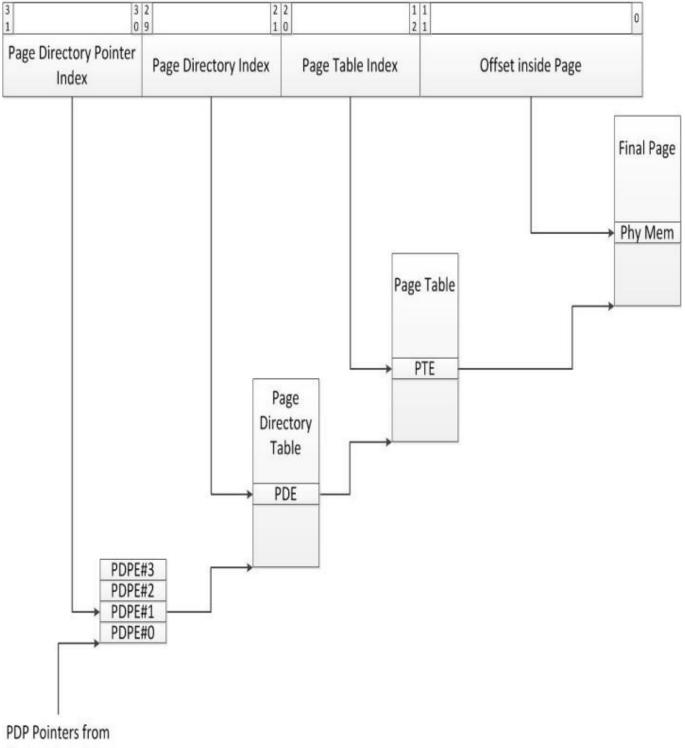

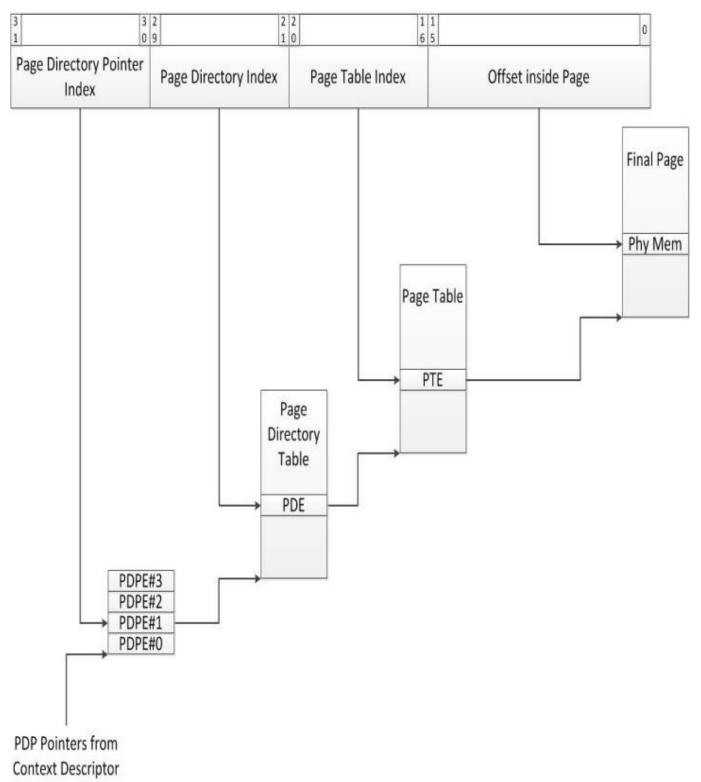

For page walk in legacy mode with 32b VA, we need 2 levels. The walk will start with a PDP pointer provided by the context descriptor and uses the GraphicsAddress as an index to consecutive levels of page tables. Hardware implements 16KB intermediate caches to limit the page walk needed to a single level to have the same sensitivity to latency as previous generations.

The following diagram shows the page walk that is needed for a 4KB page.

Context Descriptor

### Walk with 64KB Page

#### Page Table Entry (PTE) Formats

#### Page Table Entry formats for 32b VA use the following format:

| 6     6     6     5     5     5     5     5     5     5       8     2     1     0     9     8     7     6     5     4     3     2     1 | HAW-1 3 3 2 2 2 2 2 2 2 2 2 2 2 1 1 1 1 1 1 | 1 1 1 9 8 7 6 5 4 3<br>2 1 0 9 8 7 6 5 4 3 | 2 1 0         |     |

|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------|---------------|-----|

| Ignored                                                                                                                                 | Address of Page Table                       | Ignored                                    | R<br>/ P<br>W | PDE |

| Ignored                                                                                                                                 | Address of the 64KB MB page Rsvd.           |                                            | IR<br>g/P     | PTE |

| Ignored | Address of 4KB Page | Ign V I P I R P I R PTE (4KB Page) |

|---------|---------------------|------------------------------------|

|---------|---------------------|------------------------------------|

#### **PDE for Page Table**

| 6       6       6       5       5       5       5       5       5       5         3       2       1       0       9       8       7       6       5       4       3       2       1 | HAW HAW-1 | 3         3         2         2         2         2         2         2         2         2         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 | 1 1 9 8 7 6 5 4 3<br>1 0 | 2 1 0         |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------|-----|

| Ignored                                                                                                                                                                             |           | Address of page-directory-pointer-table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Ignored                  | R<br>/ P<br>W | PDE |

| Bits           | Field              | Description                                                                                                                                                                                                                 |

|----------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63:HAW*        | Ignored            | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                           |

| (HAW-<br>1):12 | ADDR:<br>Address   | Physical address of 4-KByte aligned page table referenced by this entry.<br>This field is treated as Guest Physical Address (GPA) when Nested translations are<br>enabled (NESTE=1) in the relevant extended-context entry. |

| 11:2           | Ignored            | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                           |

| 1              | R/W:<br>Read/Write | Write permission rights. If 0, write permission not granted for requests targeted to the memory range pointed by this PDE.<br>In Legacy mode with 32b VA, R/W bits from PDE are not used.                                   |

| 0              | P: Present         | PD Entry is present. It must be "1" to point to a page directory pointer table                                                                                                                                              |

\* HAW = 39 for client, and 46 for server.

### PTE: Page Table Entry for 64KB Page

| 6 6 6 6 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 | HAW HAW- | 1     3     3     2     2     2     2     2     2     2     2     2     1     1     1       1     0     9     8     7     6     5     4     3     2     1     0     9     8     7     6 | 1 1 1 1<br>5 4 3 2 | 1 1<br>1 0 | 9            | 8 7 | 6   | 5 4 | 3             | 2 1            | ι Ο |                    |

|-----------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------|--------------|-----|-----|-----|---------------|----------------|-----|--------------------|

| Ignored                                 |          | Address of the 64KB MB page                                                                                                                                                             | Rsvd.              | Ign        | N<br>U<br>II | g A | Igr | n C | P<br>W<br>D T | IF<br>g/<br>nV | P   | PTE<br>(64KB Page) |

| Bits           | Field                            | Description                                                                                                                                                                                                                                                                                                                                |

|----------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63:HAW*        | Ignored                          | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                                                                                                                                          |

| (HAW-<br>1):16 | ADDR: Address                    | Physical address of 64KB memory page referenced by this entry.<br>This field is treated as Guest Physical Address (GPA) when Nested translations are<br>enabled (NESTE=1) in the relevant extended-context entry.                                                                                                                          |

| 15:10          | Ignored                          | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                                                                                                                                          |

| 9              | N: Null                          | For Tile-Resources, private PPGTT tables enables for driver to merge Null Page information to primary (1 <sup>st</sup> Level) translation tables. If Null=1, the h/w will avoid the memory access and return all zero's for the read access with a null completion, write accesses are dropped.                                            |

| 8              | Ignored                          | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                                                                                                                                          |

| 7              | PAT: Page<br>Attribute           | For devices operating in the processor coherency domain, this field indirectly determines the memory type used to access the page directory-pointer table referenced by this entry.                                                                                                                                                        |

| 6:5            | Ignored                          | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                                                                                                                                          |

| 4              | PCD: Page level<br>cache disable | For devices operating in the processor coherency domain, this field indirectly determines the memory type used to access the page directory-pointer table referenced by this entry.                                                                                                                                                        |

| 3              | PWT: Page level<br>Write-through | For devices operating in the processor coherency domain, this field indirectly determines the memory type used to access the page directory- pointer table referenced by this entry.                                                                                                                                                       |

| 2              | Ignored                          | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                                                                                                                                          |

| 1              | R/W: Read/Write                  | Write permission rights. If 0, write permission not granted for requests with user-level privilege (and requests with supervisor-level privilege, if WPE=1 in the relevant extended-context-entry) to the memory region controlled by this entry. See a later section for access rights.<br>GPU does not support Supervisor mode contexts. |

| 0              | P: Present                       | It must be "1" to point to a 64KB Page.                                                                                                                                                                                                                                                                                                    |

\* HAW = 39 for client, and 46 for server.

### PTE: Page Table Entry for 4KB Page

| 6 6 6 5 5<br>3 2 1 0 9 8 | 5 5 5 5 5 5 5 5 5<br>8 7 6 5 4 3 2 1 | HAW       HAW-1       3       3       2       2       2       2       2       2       2       2       2       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 <th1< th="">       1       1       <th1< th="" th<=""></th1<></th1<> |

|--------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits                     | Field                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 63:HAW*                  | Ignored                              | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |